Busque con el número de pieza junto con el fabricante o la descripción

74AUP1G125 |

| Part Number | 74AUP1G125 |

| Manufacturer | DIODES (https://www.diodes.com/) |

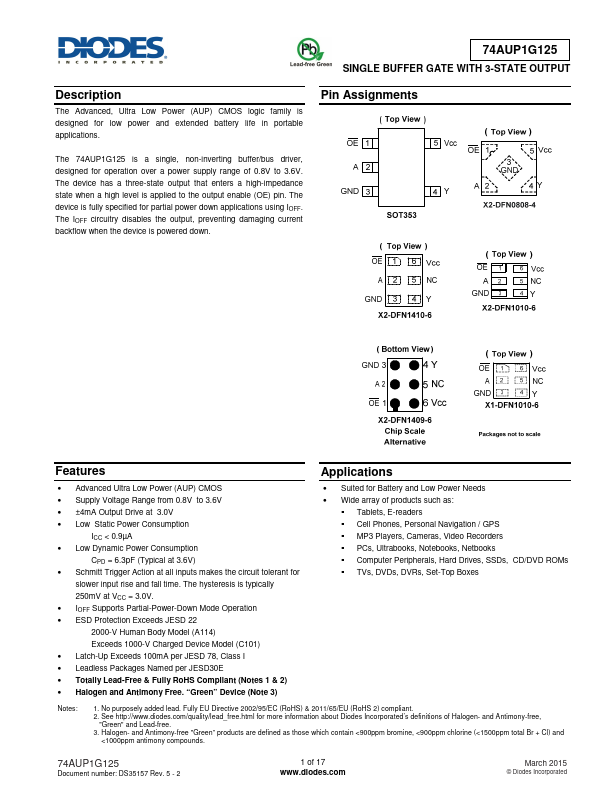

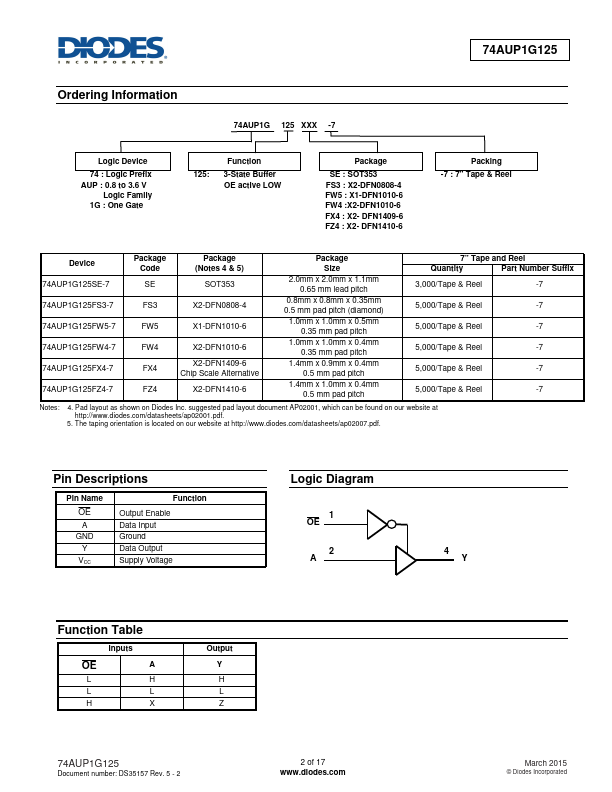

| Description | The Advanced, Ultra Low Power (AUP) CMOS logic family is designed for low power and extended battery life in portable applications. Pin Assignments The 74AUP1G125 is a single, non-inverting buffer/b... |

| Features |

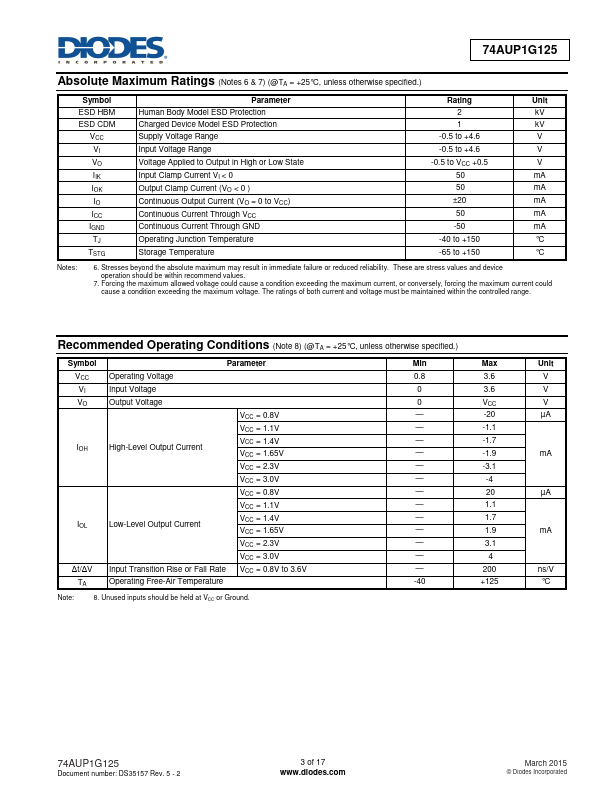

• Advanced Ultra Low Power (AUP) CMOS • Supply Voltage Range from 0.8V to 3.6V • ±4mA Output Drive at 3.0V • Low Static Power Consumption ICC < 0.9µA • Low Dynamic Power Consumption CPD = 6.3pF (Typical at 3.6V) • Schmitt Trigger Action at all inputs makes the circuit tolerant for slower input rise and fall time. The hysteresis is typically 250mV at VCC = 3.0V. • IOFF Supports Partial-Power-Down Mode Operation • ESD Protection Exceeds JESD 22 2000-V Human Body Model (A114) Exceeds 1000-V Charged Device Model (C101) • Latch-Up Exceeds 100mA per JESD 78, Class I • Leadless Packages Named per JES... |

| Document |

PDF 381.13KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74AUP1G125 |

NXP Semiconductors |

Low-power buffer/line driver |

|

| 2 | 74AUP1G125 |

nexperia |

Low-power buffer/line driver |

|

| 3 | 74AUP1G125-Q100 |

nexperia |

Low-power buffer/line driver |

|

| 4 | 74AUP1G126 |

NXP |

Low-Power buffer/line driver |

|

| 5 | 74AUP1G126 |

Diodes |

SINGLE BUFFER GATE |

|

| 6 | 74AUP1G126 |

nexperia |

Low-power buffer/line driver |

|