Busque con el número de pieza junto con el fabricante o la descripción

74F114 |

| Part Number | 74F114 |

| Manufacturer | Fairchild Semiconductor |

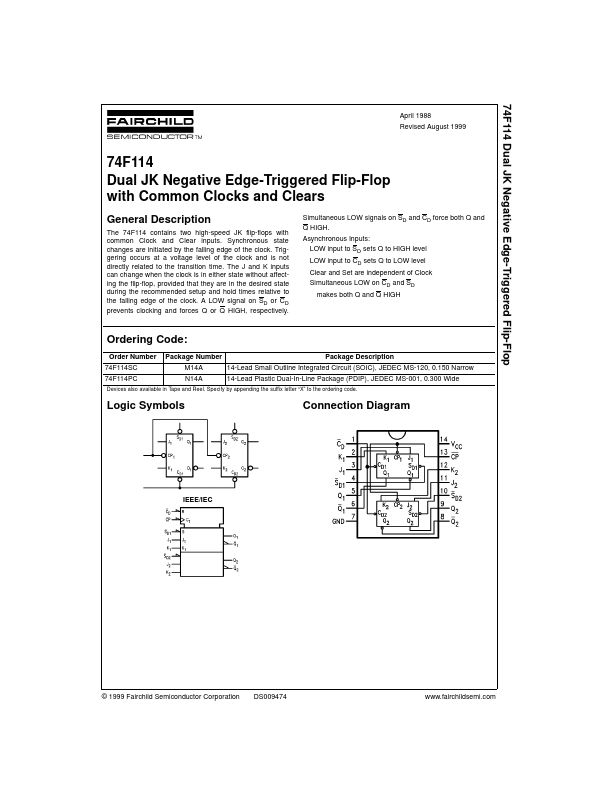

| Description | The 74F114 contains two high-speed JK flip-flops with common Clock and Clear inputs. Synchronous state changes are initiated by the falling edge of the clock. Triggering occurs at a voltage level of t... |

| Features |

Ordering Code:

Order Number 74F114SC 74F114PC Package Number M14A N14A Package Description 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Logic Symbols

Connection Diagram

IEEE/IEC

© 1999 Fairchild Semiconductor Corporation

DS009474

www.fairchildsemi.com

74F114

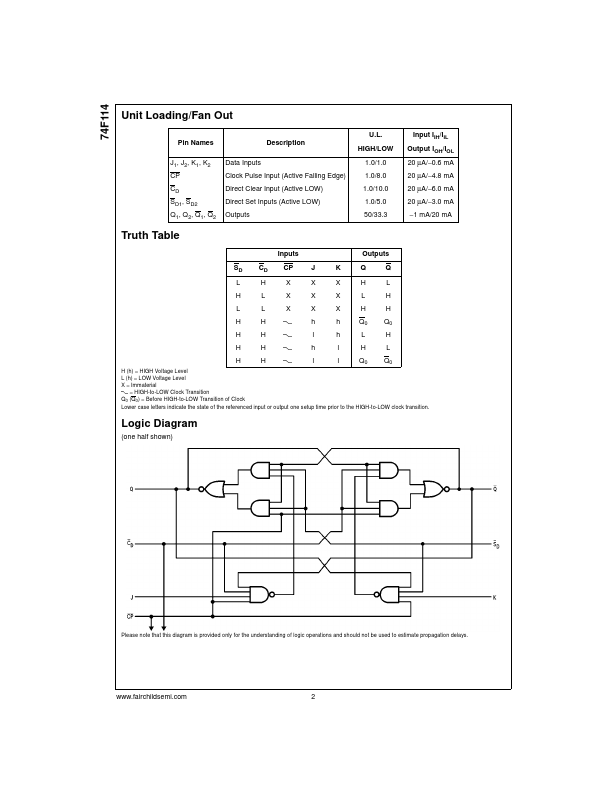

Unit Loading/Fan Out

U.L. Pin Names J1, J2, K1, K2 CP CD SD1, SD2 Q1, Q2, Q1, Q2 Data Inputs Clock Pulse Input (Active Fall... |

| Document |

PDF 55.22KB |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74F11 |

National Semiconductor |

Triple 3-Input AND Gate |

|

| 2 | 74F11 |

Fairchild Semiconductor |

Triple 3-Input AND Gate |

|

| 3 | 74F11 |

NXP |

Triple 3-input NAND gate |

|

| 4 | 74F11 |

Texas Instruments |

Triple 3-Input AND Gate |

|

| 5 | 74F112 |

NXP |

Dual J-K negative edge-triggered flip-flop |

|

| 6 | 74F112 |

Fairchild Semiconductor |

Dual JK Negative Edge-Triggered Flip-Flop |

|