Busque con el número de pieza junto con el fabricante o la descripción

74F112 |

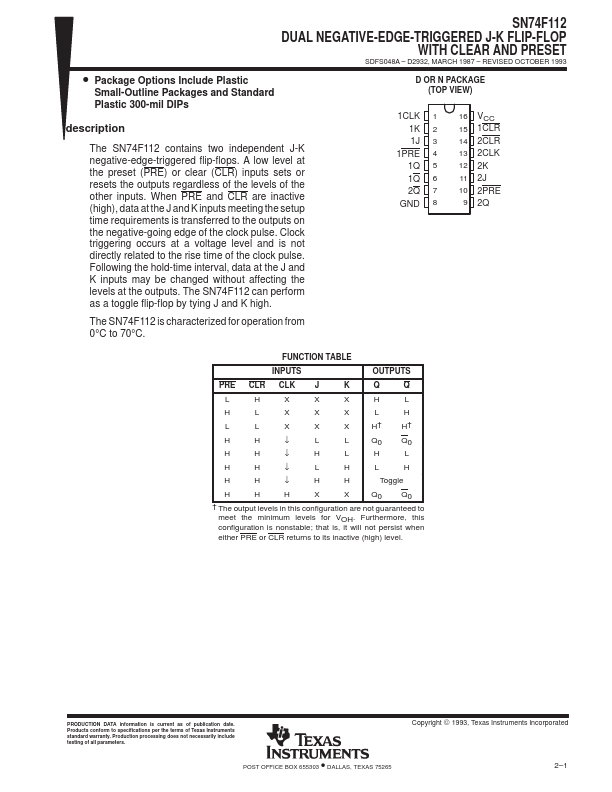

| Part Number | 74F112 |

| Manufacturer | Texas Instruments (https://www.ti.com/) |

| Description | The SN74F112 contains two independent J-K negative-edge-triggered flip-flops. A low level at the preset (PRE) or clear (CLR) inputs sets or resets the outputs regardless of the levels of the other inp... |

| Features |

14 2CLR 13 2CLK 12 2K 11 2J 10 2PRE 9 2Q

The SN74F112 is characterized for operation from 0°C to 70°C.

FUNCTION TABLE

INPUTS

OUTPUTS

PRE CLR CLK J

K

Q

Q

L

H

X

X

X

H

L

H

L

X

X

X

L

H

L

L

X

X

X

H†

H†

H

H

↓

L

L

Q0 Q0

H

H

↓

H

L

H

L

H

H

↓

L

H

L

H

H

H

↓

H

H

Toggle

H

H

H

X

X

Q0 Q0

† The output levels in this configuration are not guaranteed to

meet the minimum levels for VOH. Furthermore, this configuration is nonstable; that is, it will not persist when

either PRE or CLR returns to its inactive (high) level.

PRODUCTION DATA information... |

| Document |

PDF 666.05KB |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74F11 |

National Semiconductor |

Triple 3-Input AND Gate |

|

| 2 | 74F11 |

Fairchild Semiconductor |

Triple 3-Input AND Gate |

|

| 3 | 74F11 |

NXP |

Triple 3-input NAND gate |

|

| 4 | 74F11 |

Texas Instruments |

Triple 3-Input AND Gate |

|

| 5 | 74F112 |

NXP |

Dual J-K negative edge-triggered flip-flop |

|

| 6 | 74F112 |

Fairchild Semiconductor |

Dual JK Negative Edge-Triggered Flip-Flop |

|