Busque con el número de pieza junto con el fabricante o la descripción

R5F562TADDFK |

| Part Number | R5F562TADDFK |

| Manufacturer | Renesas (https://www.renesas.com/) |

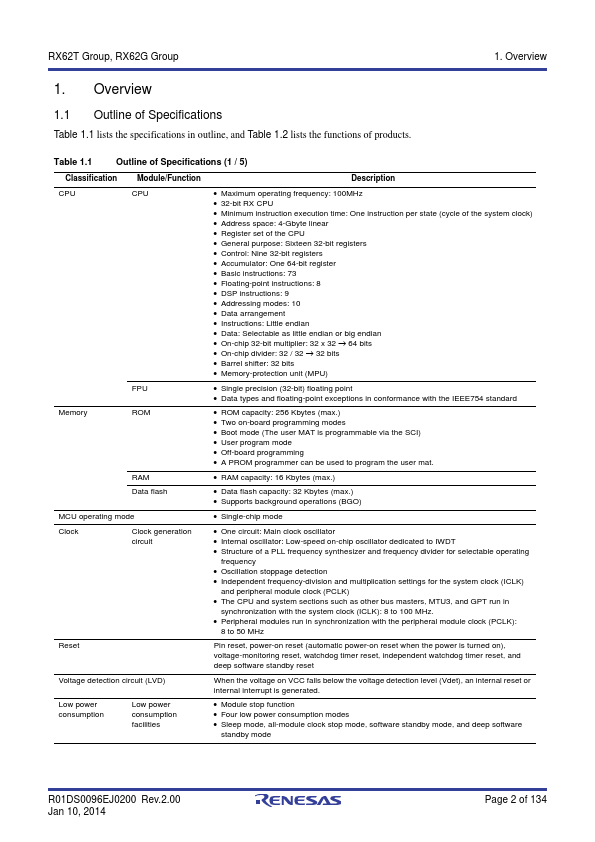

| Description | Maximum operating frequency: 100MHz 32-bit RX CPU Minimum instruction execution time: One instruction per state (cycle of the system clock) Address space: 4-Gbyte linear Register set of the CPU General purpose: Sixteen 32-bit registers Control: Nine 32-bit registers Accumulator: One 64-bit register Basic instructions: 73 Floating-point in. |

| Features |

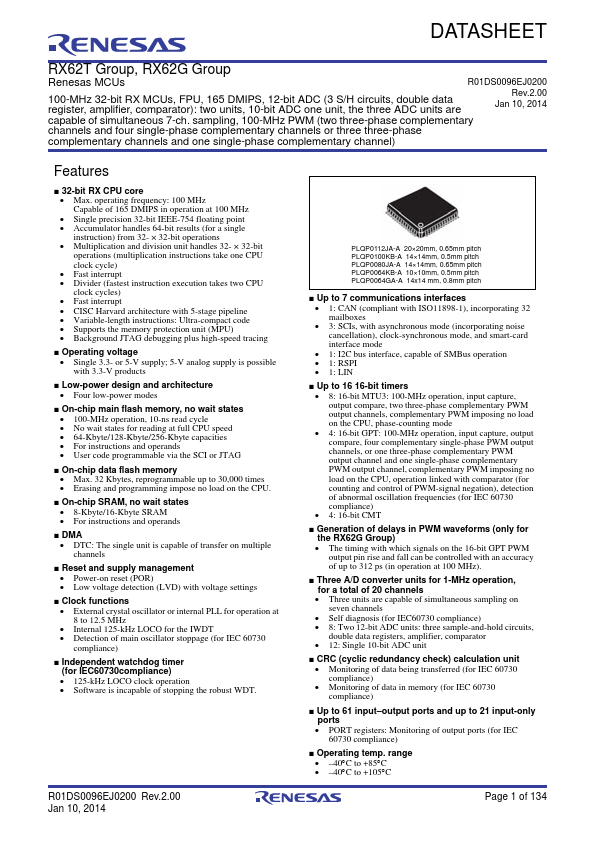

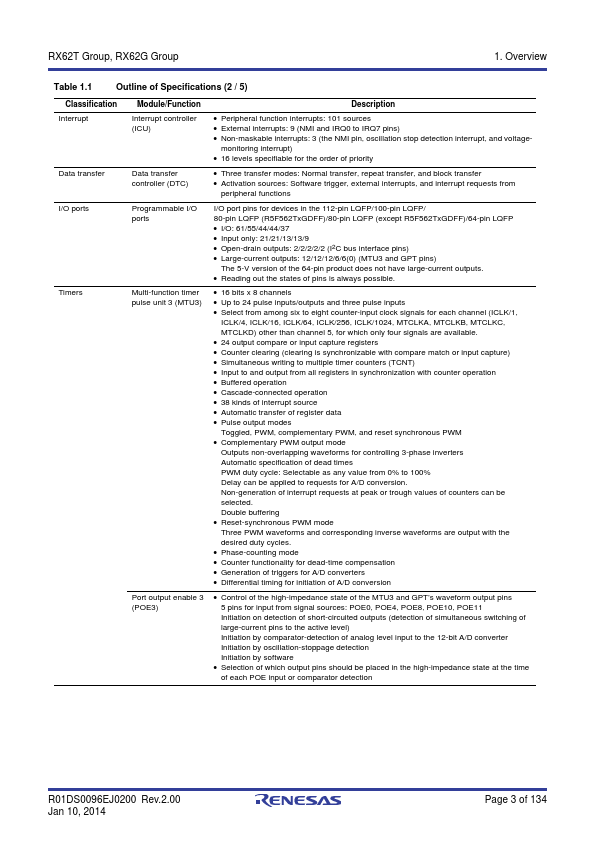

■ 32-bit RX CPU core Max. operating frequency: 100 MHz Capable of 165 DMIPS in operation at 100 MHz Single precision 32-bit IEEE-754 floating point Accumulator handles 64-bit results (for a single instruction) from 32- × 32-bit operations Multiplication and division unit handles 32- × 32-bit operations (multiplication instructions take one CPU clock cycle) Fast interrupt Divider (fastest instruction execution takes two CPU clock cycles) Fast interrupt CISC Harvard architecture with 5-stage pipeline Variable-length instructions: Ultra-compact code Supports the memory protect. |

| Datasheet |

PDF 875.57KB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | R5F562TADDFF |

Renesas |

100-MHz 32-bit RX MCUs |

|

| 2 | R5F562TADDFH |

Renesas |

100-MHz 32-bit RX MCUs |

|

| 3 | R5F562TADDFM |

Renesas |

100-MHz 32-bit RX MCUs |

|

| 4 | R5F562TADDFP |

Renesas |

100-MHz 32-bit RX MCUs |

|

| 5 | R5F562TAADFF |

Renesas |

100-MHz 32-bit RX MCUs |

|

| 6 | R5F562TAADFH |

Renesas |

100-MHz 32-bit RX MCUs |

|

| 7 | R5F562TAADFK |

Renesas |

100-MHz 32-bit RX MCUs |

|

| 8 | R5F562TAADFM |

Renesas |

100-MHz 32-bit RX MCUs |

|

| 9 | R5F562TAADFP |

Renesas |

100-MHz 32-bit RX MCUs |

|

| 10 | R5F562TAAGFF |

Renesas |

100-MHz 32-bit RX MCUs |

|