Busque con el número de pieza junto con el fabricante o la descripción

IS66WVH16M8BLL |

| Part Number | IS66WVH16M8BLL |

| Manufacturer | ISSI |

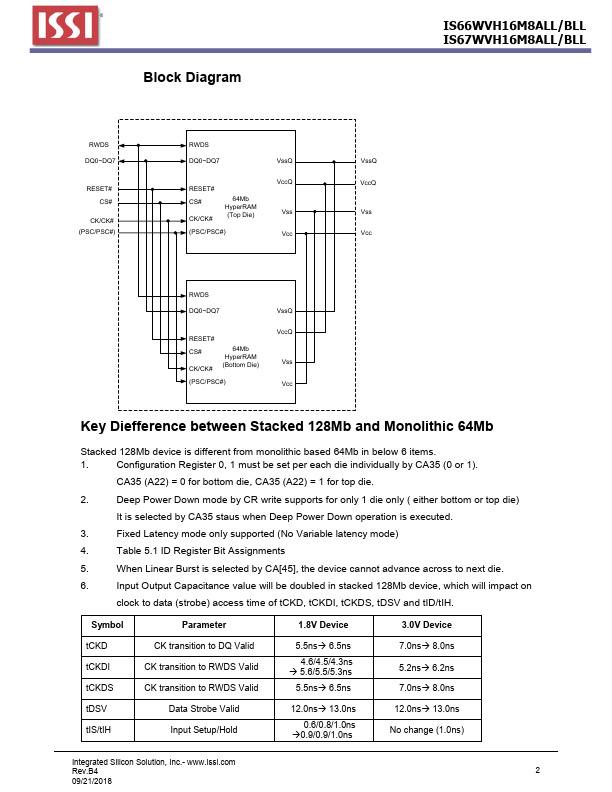

| Description | 16M x 8 HyperRAM™ IS66WVH16M8ALL/BLL IS67WVH16M8ALL/BLL 6(37(0%(5 2018 Overview The IS66/67WVH16M8ALL/BLL are integrated memory device of 128Mbit Pseudo Static Random Access Memory using a self-refresh DRAM array organized as 16M words by 8 bits. The device is a dual die stack of two 64Mb die. The device supports a HyperBus interface, Very Low Signal Count. |

| Features |

RWDS DCARS Timing – During read transactions RWDS is offset by a second clock, phase shifted from CK – The Phase Shifted Clock is used to move the RWDS transition edge within the read data eye Performance Summary Read Transaction Timings Maximum Clock Rate at 1.8V VCC/VCCQ Maximum Clock Rate at 3.0V VCC/VCCQ Maximum Access Time, (tACC at 166 MHz) Maximum CS# Access Time to first word at 166 MHz (excluding refresh latency) 166 MHz 100 MHz 36 ns 56 ns High Performance Up to 333MB/s Double-Data Rate (DDR) - two data transfers per clock 166-MHz clock rate (333 MB/s) at 1.8V VCC 100-MH. |

| Datasheet |

PDF 2.26MB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | IS66WVH16M8ALL |

ISSI |

16M x 8 HyperRAM |

|

| 2 | IS66WVH8M8ALL |

ISSI |

8M x 8 HyperRAM |

|

| 3 | IS66WVH8M8BLL |

ISSI |

8M x 8 HyperRAM |

|

| 4 | IS66WVH8M8DALL |

ISSI |

8M x 8 HyperRAM |

|

| 5 | IS66WVH8M8DBLL |

ISSI |

8M x 8 HyperRAM |

|

| 6 | IS66WVH8M8EDALL |

ISSI |

8M x 8 HyperRAM |

|

| 7 | IS66WVH8M8EDBLL |

ISSI |

8M x 8 HyperRAM |

|

| 8 | IS66WVH8M8FALL |

ISSI |

64Mb HyperRAM |

|

| 9 | IS66WVH8M8FBLL |

ISSI |

64Mb HyperRAM |

|

| 10 | IS66WV1M16DALL |

ISSI |

ULTRA LOW POWER PSEUDO CMOS STATIC RAM |

|