Busque con el número de pieza junto con el fabricante o la descripción

ICS93705 |

| Part Number | ICS93705 |

| Manufacturer | Integrated Circuit Systems |

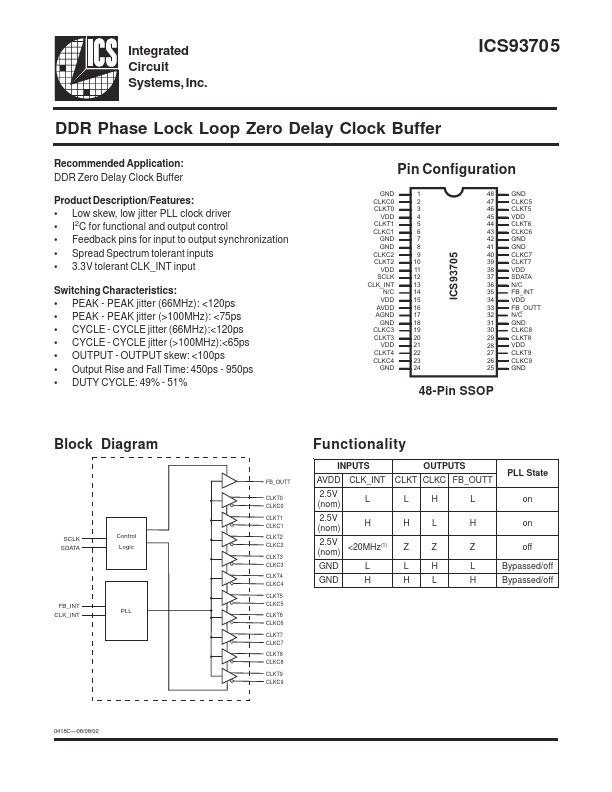

| Description | Features: • Low skew, low jitter PLL clock driver • I2C for functional and output control • Feedback pins for input to output synchronization • Spread Spectrum tolerant inputs • 3.3V tolerant CLK_INT input Switching Characteristics: • PEAK - PEAK jitter (66MHz): <120ps • PEAK - PEAK jitter (>100MHz): <75ps • CYCLE - CYCLE jitter (66MHz):<120ps • CYCLE - CYCL. |

| Features |

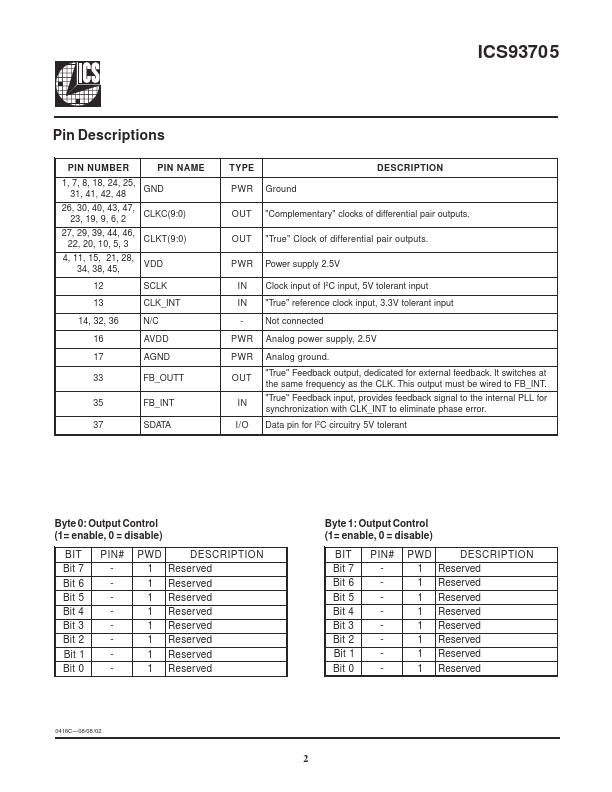

• Low skew, low jitter PLL clock driver • I2C for functional and output control • Feedback pins for input to output synchronization • Spread Spectrum tolerant inputs • 3.3V tolerant CLK_INT input Switching Characteristics: • PEAK - PEAK jitter (66MHz): <120ps • PEAK - PEAK jitter (>100MHz): <75ps • CYCLE - CYCLE jitter (66MHz):<120ps • CYCLE - CYCLE jitter (>100MHz):<65ps • OUTPUT - OUTPUT skew: <100ps • Output Rise and Fall Time: 450ps - 950ps • DUTY CYCLE: 49% - 51% GND CLKC0 CLKT0 VDD CLKT1 CLKC1 GND GND CLKC2 CLKT2 VDD SCLK CLK_INT N/C VDD AVDD AGND GND CLKC3 CLKT3 VDD CLKT4 CLKC4 GND Pi. |

| Datasheet |

PDF 65.85KB |

| Distributor | Stock | Price | Buy |

|---|

ICS93705 |

| Part Number | ICS93705 |

| Manufacturer | Renesas |

| Title | DDR Phase Lock Loop Zero Delay Clock Buffer |

| Description | Features: • Low skew, low jitter PLL clock driver • I2C for functional and output control • Feedback pins for input to output synchronization • Spread Spectrum tolerant inputs • 3.3V tolerant CLK_INT input Switching Characteristics: • PEAK - PEAK jitter (66MHz): <120ps • PEAK - PEAK jitter (>100MHz). |

| Features |

• Low skew, low jitter PLL clock driver • I2C for functional and output control • Feedback pins for input to output synchronization • Spread Spectrum tolerant inputs • 3.3V tolerant CLK_INT input Switching Characteristics: • PEAK - PEAK jitter (66MHz): <120ps • PEAK - PEAK jitter (>100MHz): <75ps • CYCLE - CYCLE jitter (66MHz):<120ps • CYCLE - CYCLE jitter (>100MHz):<65ps • OUTPUT - OUTPUT skew: . |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | ICS93701 |

Integrated Circuit Systems |

DDR Phase Lock Loop Clock Driver |

|

| 2 | ICS93716YF-T |

Integrated Circuit Systems |

Low Cost DDR Phase Lock Loop Clock Driver |

|

| 3 | ICS93716YG-T |

Integrated Circuit Systems |

Low Cost DDR Phase Lock Loop Clock Driver |

|

| 4 | ICS93732 |

Integrated Circuit Systems |

Low Cost DDR Phase Lock Loop Zero Delay Buffer |

|

| 5 | ICS93732 |

Renesas |

Low Cost DDR Phase Lock Loop Zero Delay Buffer |

|

| 6 | ICS932S200 |

Integrated Circuit Systems |

Frequency Timing Generator |

|

| 7 | ICS932S202 |

Integrated Circuit Systems |

Frequency Timing Generator |

|

| 8 | ICS932S203 |

IDT |

Frequency Generator |

|

| 9 | ICS932S203 |

Integrated Circuit Systems |

Frequency Generator |

|

| 10 | ICS932S208 |

Integrated Circuit Systems |

Programmable Timing Control Hub |

|