Busque con el número de pieza junto con el fabricante o la descripción

CY37032P44-125JI |

| Part Number | CY37032P44-125JI |

| Manufacturer | Cypress Semiconductor |

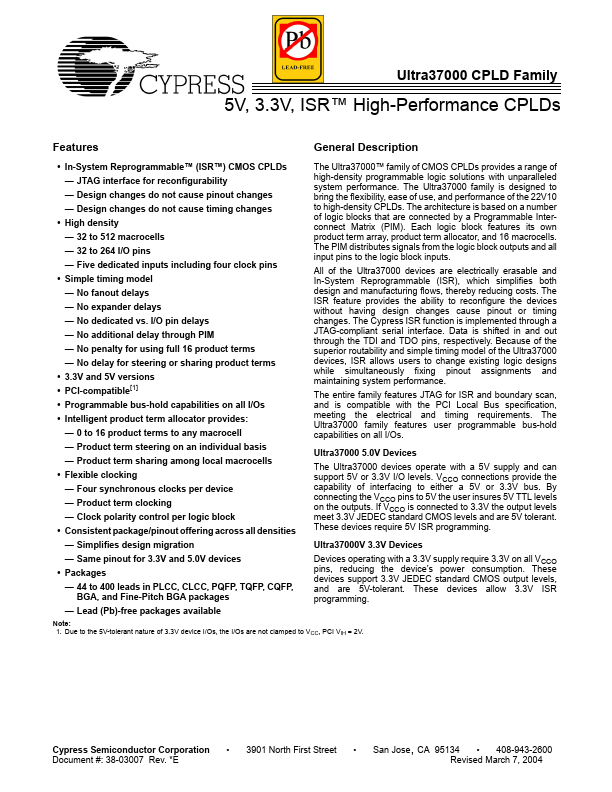

| Description | The Ultra37000™ family of CMOS CPLDs provides a range of high-density programmable logic solutions with unparalleled system performance. The Ultra37000 family is designed to bring the flexibility, ease of use, and performance of the 22V10 to high-density CPLDs. The architecture is based on a number of logic blocks that are connected by a Programmable Interco. |

| Features |

• In-System Reprogrammable™ (ISR™) CMOS CPLDs — JTAG interface for reconfigurability — Design changes do not cause pinout changes — Design changes do not cause timing changes • High density — 32 to 512 macrocells — 32 to 264 I/O pins — Five dedicated inputs including four clock pins • Simple timing model — No fanout delays — No expander delays — No dedicated vs. I/O pin delays — No additional delay through PIM — No penalty for using full 16 product terms • • • • — No delay for steering or sharing product terms 3.3V and 5V versions PCI-compatible[1] Programmable bus-hold capabilities on all I/O. |

| Datasheet |

PDF 1.55MB |

| Distributor | Stock | Price | Buy |

|---|

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | CY37032P44-125JC |

Cypress Semiconductor |

5V/ 3.3V/ ISR High-Performance CPLDs |

|

| 2 | CY37032P44-125AC |

Cypress Semiconductor |

5V/ 3.3V/ ISR High-Performance CPLDs |

|

| 3 | CY37032P44-125AI |

Cypress Semiconductor |

5V/ 3.3V/ ISR High-Performance CPLDs |

|

| 4 | CY37032P44-154AC |

Cypress Semiconductor |

5V/ 3.3V/ ISR High-Performance CPLDs |

|

| 5 | CY37032P44-154AI |

Cypress Semiconductor |

5V/ 3.3V/ ISR High-Performance CPLDs |

|

| 6 | CY37032P44-154JC |

Cypress Semiconductor |

5V/ 3.3V/ ISR High-Performance CPLDs |

|

| 7 | CY37032P44-154JI |

Cypress Semiconductor |

5V/ 3.3V/ ISR High-Performance CPLDs |

|

| 8 | CY37032P44-200AC |

Cypress Semiconductor |

5V/ 3.3V/ ISR High-Performance CPLDs |

|

| 9 | CY37032P44-200JC |

Cypress Semiconductor |

5V/ 3.3V/ ISR High-Performance CPLDs |

|

| 10 | CY37032 |

Cypress Semiconductor |

5V/ 3.3V/ ISR High-Performance CPLDs |

|