Busque con el número de pieza junto con el fabricante o la descripción

74LVX125 |

| Part Number | 74LVX125 |

| Manufacturer | National Semiconductor |

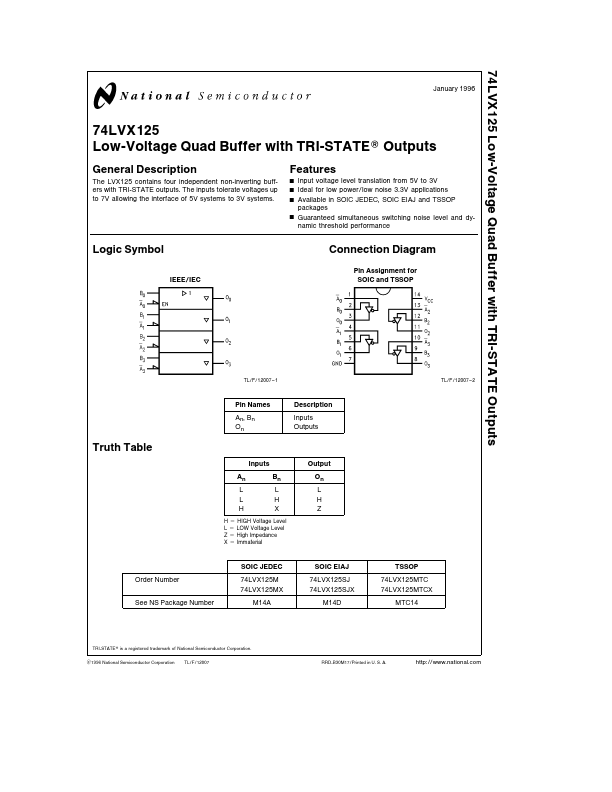

| Description | The LVX125 contains four independent non-inverting buffers with TRI-STATE outputs The inputs tolerate voltages up to 7V allowing the interface of 5V systems to 3V systems Features Y Input voltage level translation from 5V to 3V Y Ideal for low power low noise 3 3V applications Y Available in SOIC JEDEC SOIC EIAJ and TSSOP packages Y Guaranteed simultaneous . |

| Features |

Y Input voltage level translation from 5V to 3V Y Ideal for low power low noise 3 3V applications Y Available in SOIC JEDEC SOIC EIAJ and TSSOP

packages Y Guaranteed simultaneous switching noise level and dy-

namic threshold performance

Logic Symbol

Connection Diagram

IEEE IEC

Pin Assignment for SOIC and TSSOP

TL F 12007 – 1 Truth Table Pin Names An Bn On Description Inputs Outputs Inputs An Bn LL LH HX H e HIGH Voltage Level L e LOW Voltage Level Z e High Impedance X e Immaterial Output On L H Z Order Number See NS Package Number SOIC JEDEC 74LVX125M 74LVX125MX M14A SOIC EIAJ 74L. |

| Datasheet |

PDF 114.77KB |

| Distributor | Stock | Price | Buy |

|---|

74LVX125 |

| Part Number | 74LVX125 |

| Manufacturer | Fairchild Semiconductor |

| Title | Low Voltage Quad Buffer |

| Description | The LVX125 contains four independent non-inverting buffers with 3-STATE outputs. The inputs tolerate voltages up to 7V allowing the interface of 5V systems to 3V systems. Ordering Information Order Number 74LVX125M 74LVX125SJ 74LVX125MTC Package Number M14A M14D MTC14 Package Description 14-Lead. |

| Features |

■ Input voltage level translation from 5V to 3V ■ Ideal for low power/low noise 3.3V applications ■ Guaranteed simultaneous switching noise level and dynamic threshold performance General Description The LVX125 contains four independent non-inverting buffers with 3-STATE outputs. The inputs tolerate voltages up to 7V allowing the interface of 5V systems to 3V systems. Ordering Information Order. |

74LVX125 |

| Part Number | 74LVX125 |

| Manufacturer | STMicroelectronics |

| Title | LOW VOLTAGE QUAD BUS BUFFERS |

| Description | The 74LVX125 is a low voltage CMOS QUAD BUS BUFFERs fabricated with sub-micron silicon gate and double-layer metal wiring C2MOS technology. It is ideal for low power, battery operated and low noise 3.3V applications. Figure 1: Pin Connection And IEC Logic Symbols This device requires the 3-STATE co. |

| Features | o be set high to place the output into the high impedance state. Power down protection is provided on all inputs and 0 to 7V can be accepted on inputs with no regard to the supply voltage. This device can be used to interface 5V to 3V. It combines high speed performance with the true CMOS low power consumption. All inputs and outputs are equipped with protection circuits against static discharge, . |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74LVX112 |

Fairchild Semiconductor |

Low Voltage Dual J-K Flip-Flops |

|

| 2 | 74LVX132 |

Fairchild Semiconductor |

Low Voltage Quad 2-Input NAND Schmitt Trigger |

|

| 3 | 74LVX138 |

Fairchild Semiconductor |

Low Voltage 1-of-8 Decoder/Demultiplexer |

|

| 4 | 74LVX14 |

Fairchild Semiconductor |

Low Voltage Hex Inverter |

|

| 5 | 74LVX14 |

ON Semiconductor |

LOW-VOLTAGE CMOS |

|

| 6 | 74LVX14 |

Motorola Inc |

LOW-VOLTAGE CMOS |

|

| 7 | 74LVX14 |

Toshiba Semiconductor |

HEX SCHMITT INVERTER |

|

| 8 | 74LVX157 |

Fairchild Semiconductor |

Low Voltage Quad 2-Input Multiplexer |

|

| 9 | 74LVX161284 |

Fairchild Semiconductor |

Low Voltage IEEE 161284 Translating Transceiver |

|

| 10 | 74LVX161284A |

Fairchild Semiconductor |

Low Voltage IEEE 161284 Translating Transceiver |

|