Busque con el número de pieza junto con el fabricante o la descripción

74HC180 |

| Part Number | 74HC180 |

| Manufacturer | Hitachi Semiconductor |

| Description | This universal, monolithic, 9-bit (8 data bits plus 1 parity bit) parity generator/checker features odd/even outputs and control inputs to facilitate operation in either odd or even parity application... |

| Features |

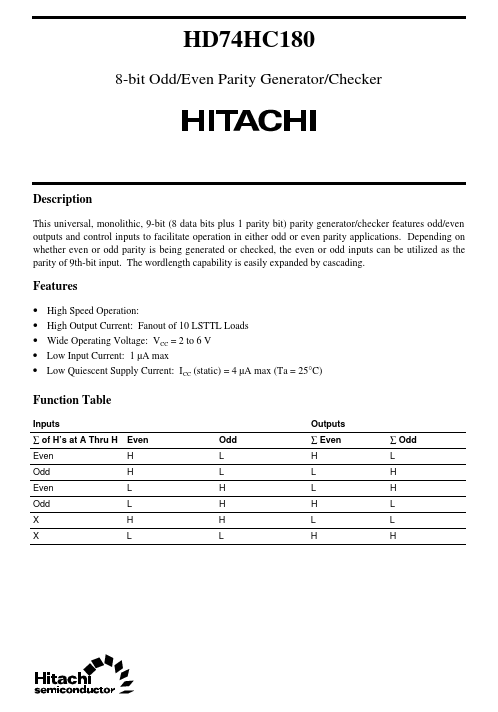

odd/even outputs and control inputs to facilitate operation in either odd or even parity applications. Depending on whether even or odd parity is being generated or checked, the even or odd inputs can be utilized as the parity of 9th-bit input. The wordlength capability is easily expanded by cascading.

Features

• High Speed Operation: • High Output Current: Fanout of 10 LSTTL Loads • Wide Operating Voltage: VCC = 2 to 6 V • Low Input Current: 1 µA max • Low Quiescent Supply Current: ICC (static) = 4 µA max (Ta = 25°C) Function Table Inputs ∑ of H’s at A Thru H Even Even H Odd H Even L ... |

| Document |

PDF 42.22KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74HC181 |

Philips |

4-bit arithmetic logic |

|

| 2 | 74HC182 |

Philips |

Look-ahead carry generator |

|

| 3 | 74HC10 |

Philips |

Triple 3-input NAND gate |

|

| 4 | 74HC10 |

Texas Instruments |

Triple 3-Input NAND Gates |

|

| 5 | 74HC10 |

nexperia |

Triple 3-input NAND gate |

|

| 6 | 74HC10-Q100 |

nexperia |

Triple 3-input NAND gate |

|