Busque con el número de pieza junto con el fabricante o la descripción

CED61A3 |

| Part Number | CED61A3 |

| Manufacturer | Chino-Excel Technology |

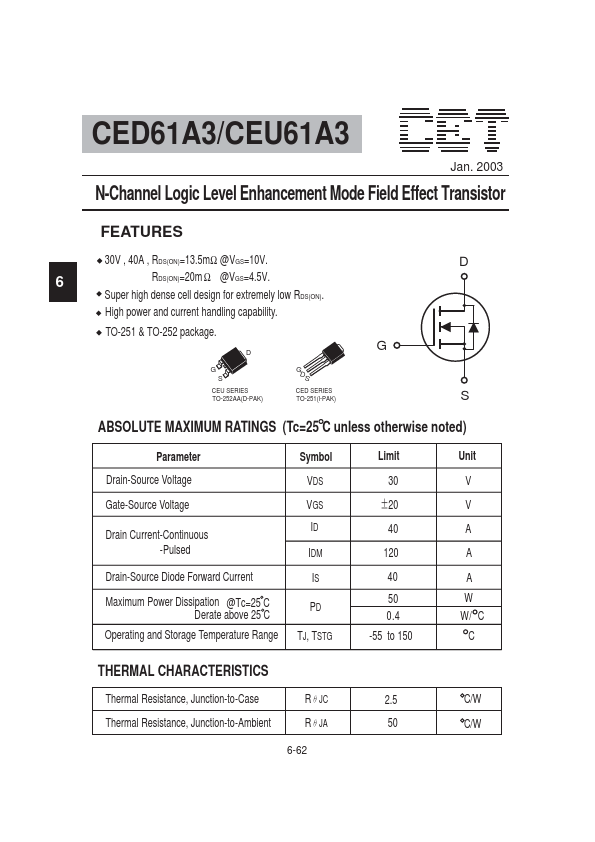

| Description | CED61A3/CEU61A3 Jan. 2003 N-Channel Logic Level Enhancement Mode Field Effect Transistor FEATURES 6 30V , 40A , RDS(ON)=13.5mΩ @VGS=10V. RDS(ON)=20m Ω @VGS=4.5V. Super high dense cell design for extr... |

| Features |

6

30V , 40A , RDS(ON)=13.5mΩ @VGS=10V. RDS(ON)=20m Ω @VGS=4.5V. Super high dense cell design for extremely low RDS(ON). High power and current handling capability. TO-251 & TO-252 package.

D G S

G D S

D

G

CEU SERIES TO-252AA(D-PAK)

CED SERIES TO-251(l-PAK)

S

ABSOLUTE MAXIMUM RATINGS (Tc=25 C unless otherwise noted)

Parameter Drain-Source Voltage Gate-Source Voltage Drain Current-Continuous -Pulsed Drain-Source Diode Forward Current Maximum Power Dissipation @Tc=25 C Derate above 25 C Operating and Storage Temperature Range Symbol VDS VGS ID IDM IS PD TJ, TSTG Limit 30 Unit V V A A A W W/... |

| Document |

PDF 42.09KB |

Similar Datasheet