Busque con el número de pieza junto con el fabricante o la descripción

HD74ACT112 |

| Part Number | HD74ACT112 |

| Manufacturer | Hitachi Semiconductor |

| Description | The HD74AC112/HD74ACT112 features individual J, K, Clock and asynchronous Set and Clear inputs to each flip-flop. When the clock goes High, the inputs are enabled and data will be accepted. The logic ... |

| Features |

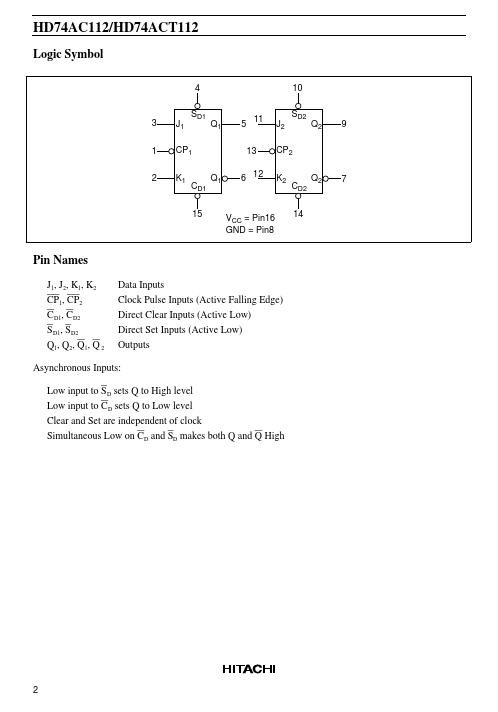

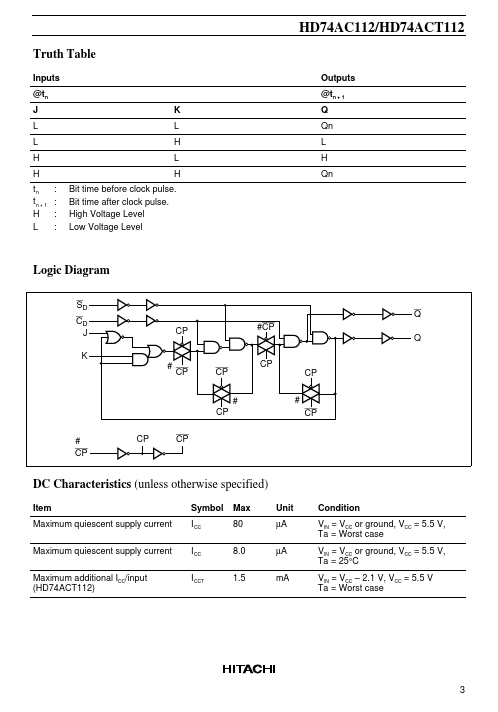

individual J, K, Clock and asynchronous Set and Clear inputs to each flip-flop. When the clock goes High, the inputs are enabled and data will be accepted. The logic level of the J and K inputs may change when the clock is High and the bistable will perform according to the Truth Table as long as minimum setup and hold times are observed. Input data is transferred to the outputs on the falling edge of the clock pulse.

Features

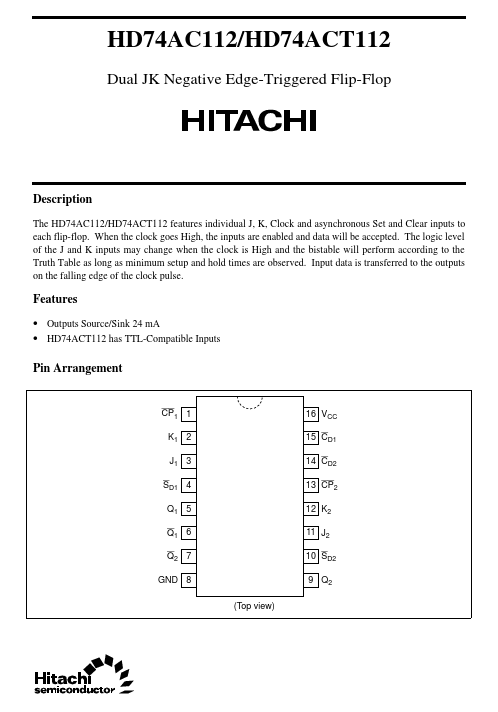

• Outputs Source/Sink 24 mA • HD74ACT112 has TTL-Compatible Inputs Pin Arrangement CP1 1 K1 2 J1 3 SD1 4 Q1 5 Q1 6 Q2 7 GND 8 (Top view) 16 VCC 15 CD1 14 CD2 13 CP2 ... |

| Document |

PDF 59.65KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | HD74ACT112 |

Renesas |

Dual JK Negative Edge-Triggered Flip-Flop |

|

| 2 | HD74ACT107 |

Hitachi Semiconductor |

Dual JK Flip-Flop (with Separate Clear and Clock) |

|

| 3 | HD74ACT107 |

Renesas |

Dual JK Flip-Flop |

|

| 4 | HD74ACT125 |

Hitachi Semiconductor |

Quad Buffer/Line Driver with 3-State Output |

|

| 5 | HD74ACT125 |

Renesas |

Quad Buffer/Line Driver |

|

| 6 | HD74ACT126 |

Hitachi Semiconductor |

Quad Buffer/Line Driver with 3-State Output |

|