Busque con el número de pieza junto con el fabricante o la descripción

LP62S16128BU-70LLI |

| Part Number | LP62S16128BU-70LLI |

| Manufacturer | AMIC Technology |

| Description | The LP62S16128B-I is a low operating current 2,097,152bit static random access memory organized as 131,072 words by 16 bits and operates on low power voltage from 2.7V to 3.6V. It is built using AMIC'... |

| Features |

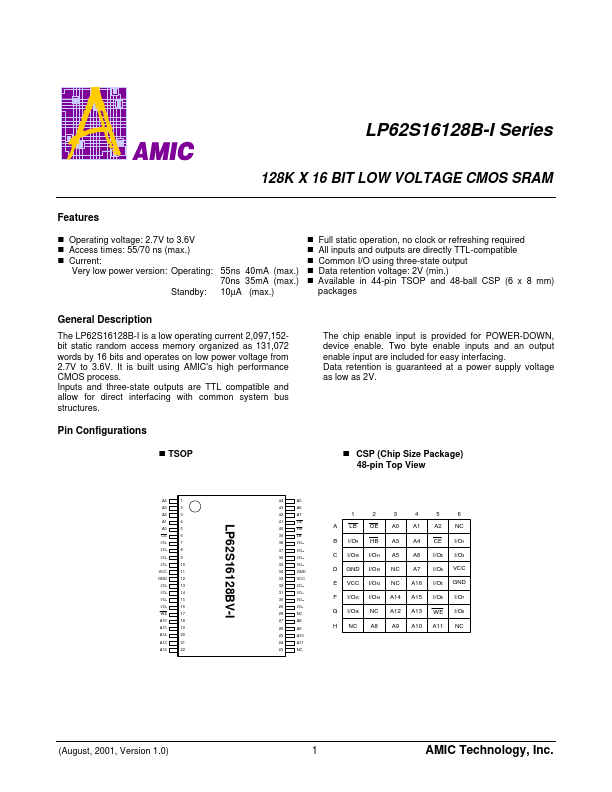

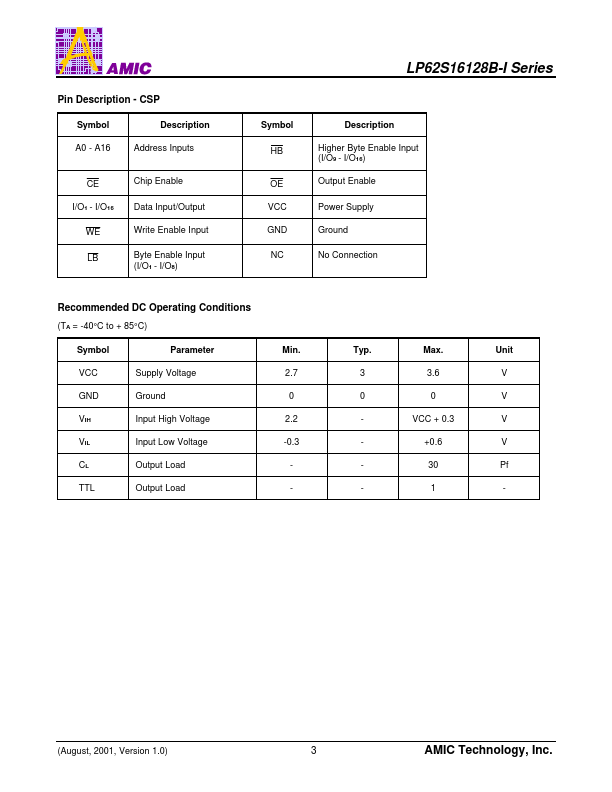

n Operating voltage: 2.7V to 3.6V n Access times: 55/70 ns (max.) n Current: Very low power version: Operating: 55ns 40mA (max.) 70ns 35mA (max.) Standby: 10µA (max.) n n n n n Full static operation, no clock or refreshing required All inputs and outputs are directly TTL-compatible Common I/O using three-state output Data retention voltage: 2V (min.) Available in 44-pin TSOP and 48-ball CSP (6 x 8 mm) packages

General Description

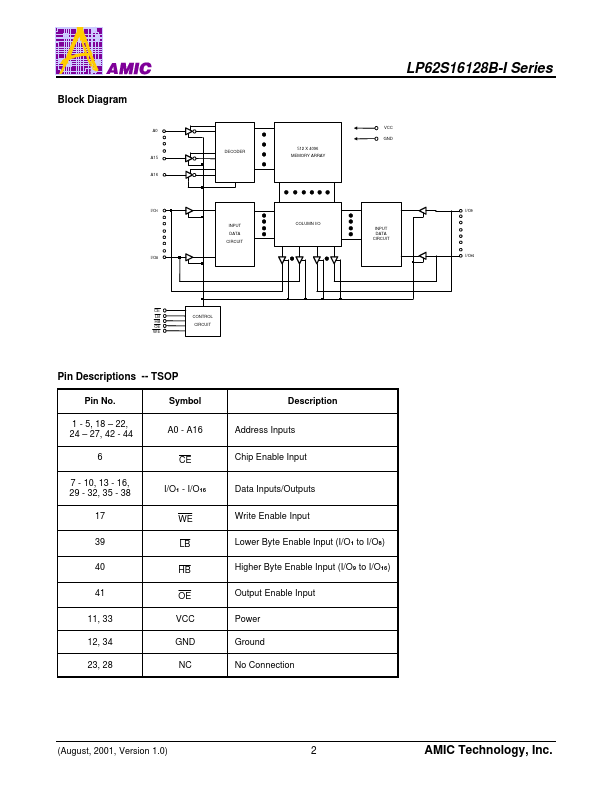

The LP62S16128B-I is a low operating current 2,097,152bit static random access memory organized as 131,072 words by 16 bits and operates on low power voltage from 2.... |

| Document |

PDF 160.12KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | LP62S16128BU-70LLT |

AMIC Technology |

128K X 16 BIT LOW VOLTAGE CMOS SRAM |

|

| 2 | LP62S16128BU-55LLI |

AMIC Technology |

128K X 16 BIT LOW VOLTAGE CMOS SRAM |

|

| 3 | LP62S16128BU-55LLT |

AMIC Technology |

128K X 16 BIT LOW VOLTAGE CMOS SRAM |

|

| 4 | LP62S16128B-I |

AMIC Technology |

128K X 16 BIT LOW VOLTAGE CMOS SRAM |

|

| 5 | LP62S16128B-T |

AMIC Technology |

128K X 16 BIT LOW VOLTAGE CMOS SRAM |

|

| 6 | LP62S16128BV-55LLI |

AMIC Technology |

128K X 16 BIT LOW VOLTAGE CMOS SRAM |

|