Busque con el número de pieza junto con el fabricante o la descripción

HYB18T512161B2F-20 |

| Part Number | HYB18T512161B2F-20 |

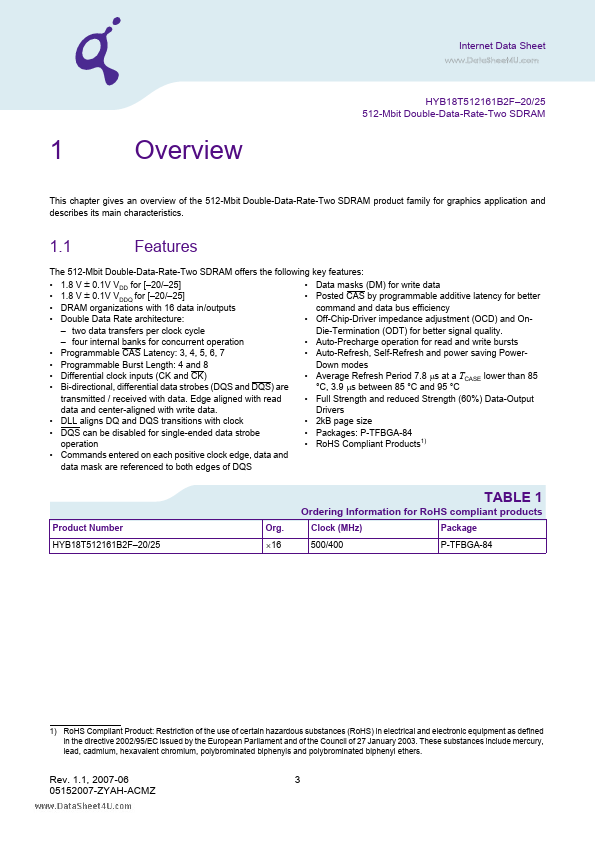

| Manufacturer | Qimonda AG |

| Description | All of the control and address inputs are synchronized with a pair of externally supplied differential clocks. Inputs are latched at the cross point of differential clocks (CK rising and CK falling). ... |

| Features |

The 512-Mbit Double-Data-Rate-Two SDRAM offers the following key features: • Data masks (DM) for write data • 1.8 V ± 0.1V VDD for [ –20/ –25] • 1.8 V ± 0.1V VDDQ for [ –20/ –25] • Posted CAS by programmable additive latency for better • DRAM organizations with 16 data in/outputs command and data bus efficiency • Double Data Rate architecture: • Off-Chip-Driver impedance adjustment (OCD) and On – two data transfers per clock cycle Die-Termination (ODT) for better signal quality. – four internal banks for concurrent operation • Auto-Precharge operation for read and write bursts • Programmable CAS L... |

| Document |

PDF 1.30MB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | HYB18T512161B2F-25 |

Qimonda AG |

512-Mbit x16 DDR2 SDRAM |

|

| 2 | HYB18T512161BF |

Qimonda AG |

512-Mbit x16 DDR2 SDRAM |

|

| 3 | HYB18T512160A |

Infineon Technologies AG |

512-Mbit Double-Data-Rate-Two SDRAM |

|

| 4 | HYB18T512160AC-3.7 |

Infineon |

512-Mbit Double-Data-Rate-Two SDRAM |

|

| 5 | HYB18T512160AC-5 |

Infineon |

512-Mbit Double-Data-Rate-Two SDRAM |

|

| 6 | HYB18T512160AF |

Infineon Technologies AG |

512-Mbit DDR2 SDRAM |

|