Busque con el número de pieza junto con el fabricante o la descripción

AS4DDR232M72PBG |

| Part Number | AS4DDR232M72PBG |

| Manufacturer | Austin Semiconductor |

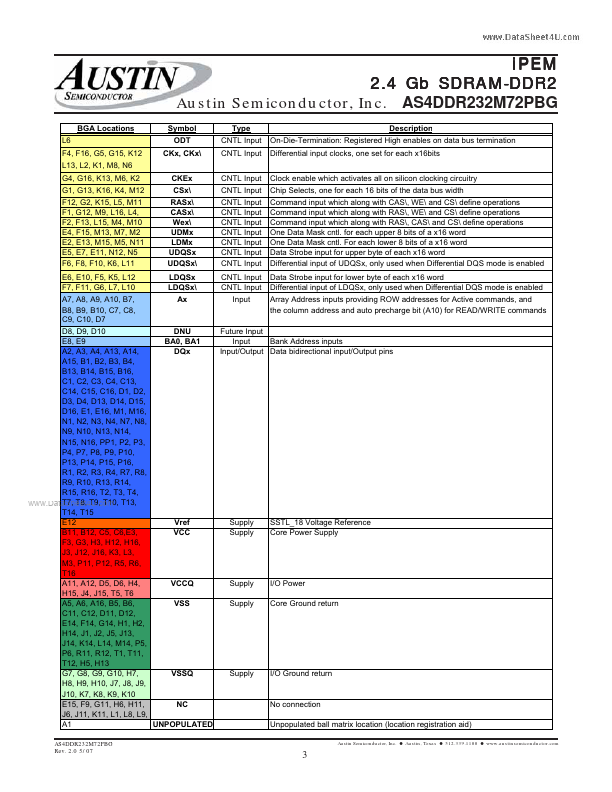

| Description | On-Die-Termination: Registered High enables on data bus termination Differential input clocks, one set for each x16bits A7, A8, A9, A10, B7, Ax Input B8, B9, B10, C7, C8, C9, C10, D7 D8, D9, D10 DNU ... |

| Features |

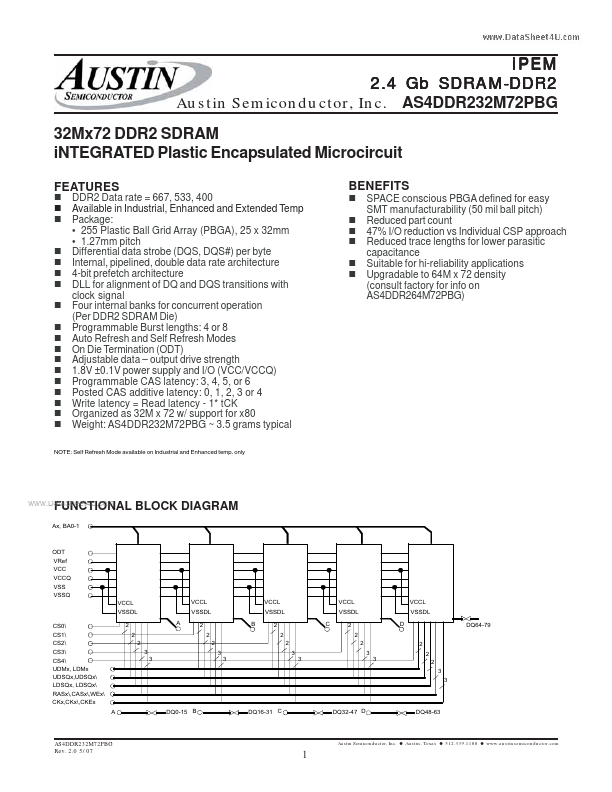

DDR2 Data rate = 667, 533, 400 Available in Industrial, Enhanced and Extended Temp Package: • 255 Plastic Ball Grid Array (PBGA), 25 x 32mm • 1.27mm pitch Differential data strobe (DQS, DQS#) per byte Internal, pipelined, double data rate architecture 4-bit prefetch architecture DLL for alignment of DQ and DQS transitions with clock signal Four internal banks for concurrent operation (Per DDR2 SDRAM Die) Programmable Burst lengths: 4 or 8 Auto Refresh and Self Refresh Modes On Die Termination (ODT) Adjustable data – output drive strength 1.8V ±0.1V power sup... |

| Document |

PDF 290.32KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | AS4DDR232M64PBG |

Micross |

32M x 64 DDR2 SDRAM |

|

| 2 | AS4DDR232M64PBG |

Austin Semiconductor |

32Mx64 DDR2 SDRAM iNTEGRATED Plastic Encapsulated Microcircuit |

|

| 3 | AS4DDR264M64PBG1 |

Austin Semiconductor |

64Mx64 DDR2 SDRAM w/ SHARED CONTROL BUS iNTEGRATED Plastic Encapsulated Microcircuit |

|

| 4 | AS4DDR264M65PBG1 |

Austin Semiconductor |

64Mx64 DDR2 SDRAM w/ DUAL CONTROL BUS iNTEGRATED Plastic Encapsulated Microcircuit |

|

| 5 | AS4DDR264M72PBG |

Austin Semiconductor |

64Mx72 DDR2 SDRAM iNTEGRATED Plastic Encapsulated Microcircuit |

|

| 6 | AS4DDR264M72PBG1 |

Micross |

4.8 Gb SDRAM-DDR2 |

|