Busque con el número de pieza junto con el fabricante o la descripción

IDTCSPU877D |

| Part Number | IDTCSPU877D |

| Manufacturer | Integrated Device Technology |

| Description | IDTCSPU877D • 1 to 10 differential clock distribution • Optimized for clock distribution in DDR2 (Double Data Rate) SDRAM applications • Operating frequency: 125MHz to 340MHz • Very low skew: ≤40ps... |

| Features |

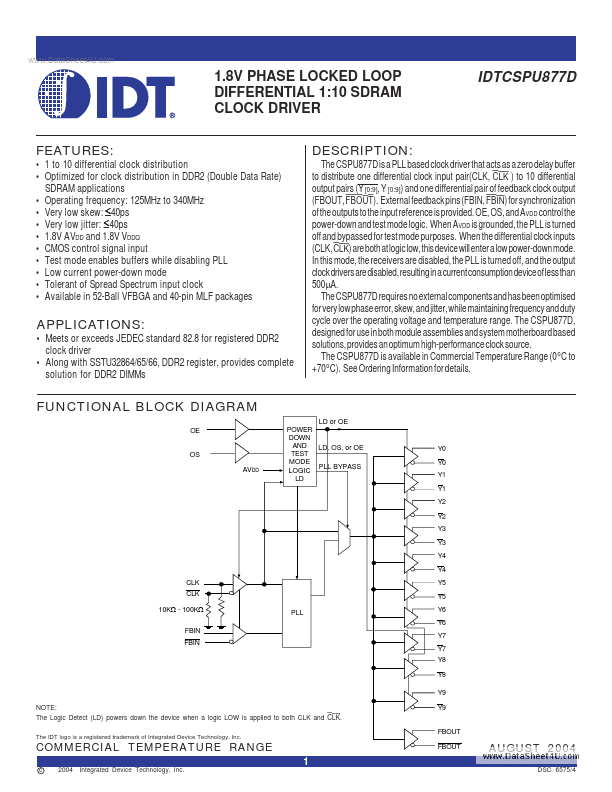

DESCRIPTION:

IDTCSPU877D

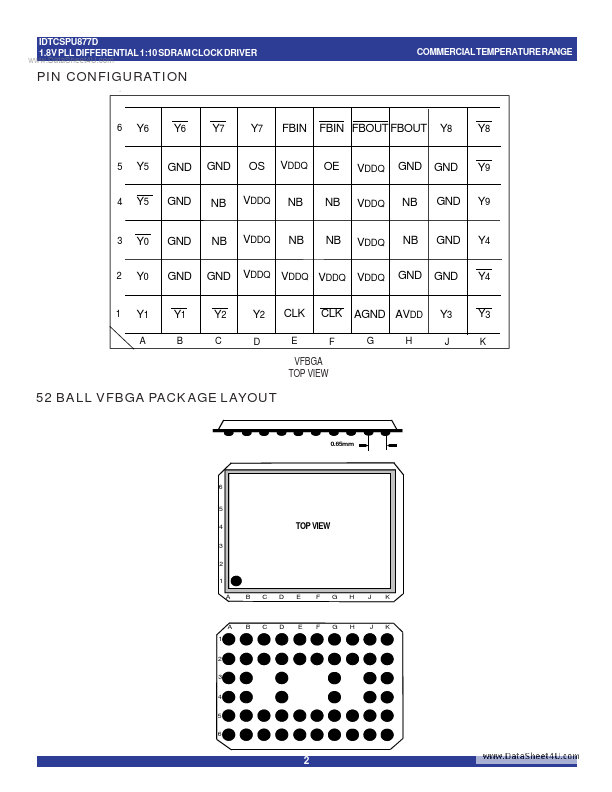

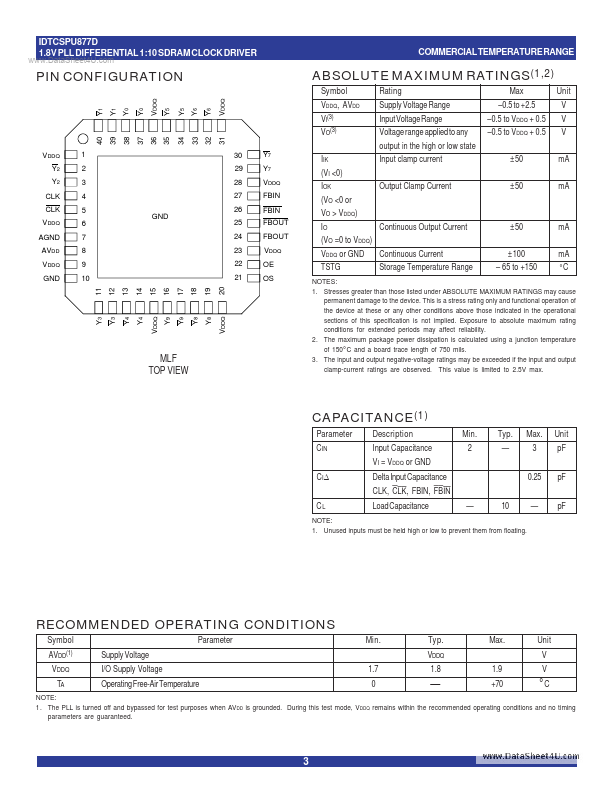

• 1 to 10 differential clock distribution • Optimized for clock distribution in DDR2 (Double Data Rate) SDRAM applications • Operating frequency: 125MHz to 340MHz • Very low skew: ≤40ps • Very low jitter: ≤40ps • 1.8V AVDD and 1.8V VDDQ • CMOS control signal input • Test mode enables buffers while disabling PLL • Low current power-down mode • Tolerant of Spread Spectrum input clock • Available in 52-Ball VFBGA and 40-pin MLF packages APPLICATIONS: • Meets or exceeds JEDEC standard 82.8 for registered DDR2 clock driver • Along with SSTU32864/65/66, DDR2 register, p... |

| Document |

PDF 179.41KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | IDTCSPU877A |

Integrated Device Technology |

1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

|

| 2 | IDTCSPUA877A |

Integrated Device Technology |

1.8V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER |

|

| 3 | IDTCSP2510C |

Integrated Device |

3.3V PHASE-LOCK LOOP CLOCK DRIVER ZERO DELAY BUFFER |

|

| 4 | IDTCSP2510D |

IDT |

3.3V PHASE-LOCK LOOP CLOCK DRIVER |

|

| 5 | IDTCSPF2510C |

Integrated Device Technology |

3.3V PHASE-LOCK LOOP CLOCK DRIVER |

|

| 6 | IDTCSPT855 |

Integrated Device Technology |

2.5V PHASE LOCKED LOOP CLOCK DRIVER |

|