Busque con el número de pieza junto con el fabricante o la descripción

HYB25D512400DF |

| Part Number | HYB25D512400DF |

| Manufacturer | Qimonda |

| Description | Read and write accesses to the DDR SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the r... |

| Features |

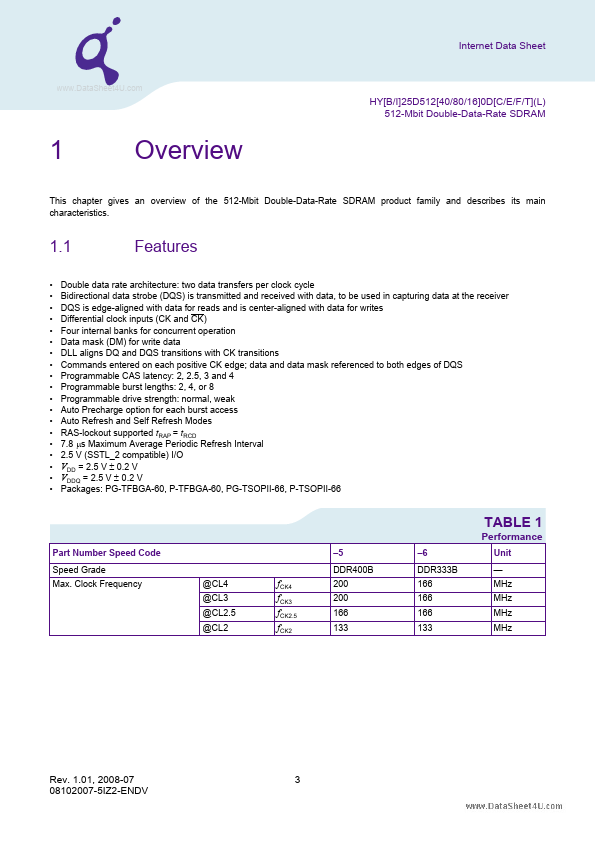

Double data rate architecture: two data transfers per clock cycle Bidirectional data strobe (DQS) is transmitted and received with data, to be used in capturing data at the receiver DQS is edge-aligned with data for reads and is center-aligned with data for writes Differential clock inputs (CK and CK) Four internal banks for concurrent operation Data mask (DM) for write data DLL aligns DQ and DQS transitions with CK transitions Commands entered on each positive CK edge; data and data mask referenced to both edges of DQS Programmable CAS latency: 2, 2.5, 3 and 4 Programmable burst lengths: 2, ... |

| Document |

PDF 2.42MB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | HYB25D512400DE |

Qimonda |

512M DDR SDRAM |

|

| 2 | HYB25D512400DT |

Qimonda |

512M DDR SDRAM |

|

| 3 | HYB25D512400AT |

Infineon Technologies AG |

512Mbit Double Data Rate SDRAM |

|

| 4 | HYB25D512400BC |

Infineon |

512Mbit Double Data Rate SDRAM |

|

| 5 | HYB25D512400BC |

Qimonda |

(HYB25D512xx0Bx) 512-Mbit Double-Data-Rate SDRAM |

|

| 6 | HYB25D512400BE |

Infineon |

512Mbit Double Data Rate SDRAM |

|