Busque con el número de pieza junto con el fabricante o la descripción

NB100LVEP222 |

| Part Number | NB100LVEP222 |

| Manufacturer | ON Semiconductor (https://www.onsemi.com/) |

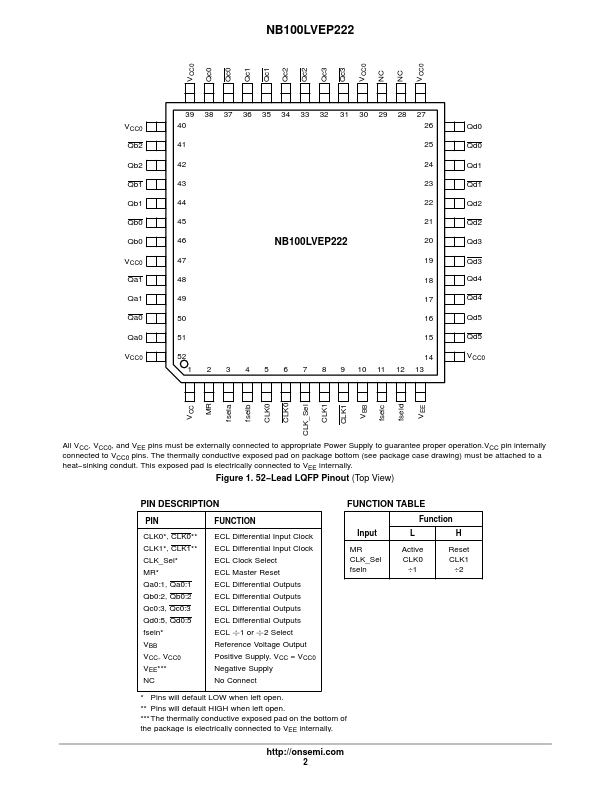

| Description | PIN CLK0*, CLK0** CLK1*, CLK1** CLK_Sel* MR* Qa0:1, Qa0:1 Qb0:2, Qb0:2 Qc0:3, Qc0:3 Qd0:5, Qd0:5 fseln* VBB VCC, VCC0 VEE*** NC FUNCTION ECL Differential Input Clock ECL Differential Input Clock ECL C... |

| Features |

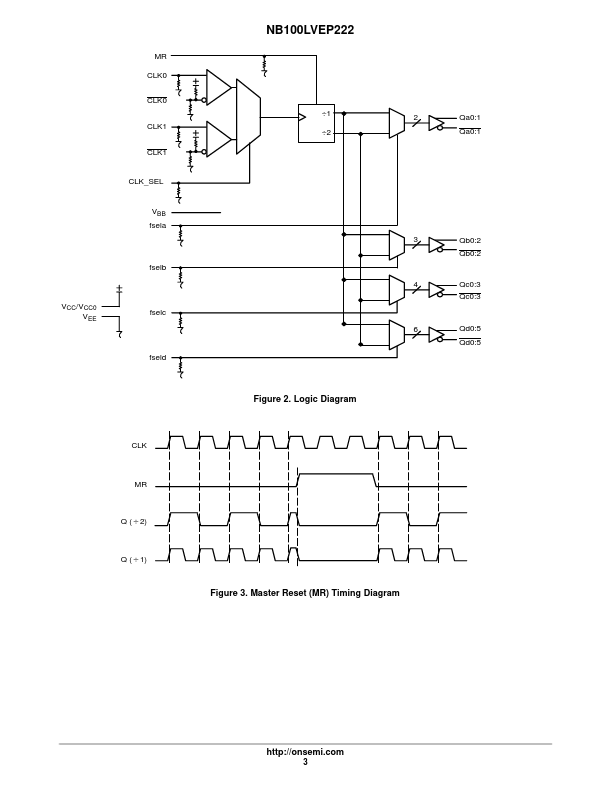

erminate output states requiring an MR pulse to resynchronize any 1/2X outputs (See Figure 3). Unused output pairs should be left unterminated (open) to reduce power and switching noise. The NB100LVEP222, as with most ECL devices, can be operated from a positive VCC/VCC0 supply in LVPECL mode. This allows the LVEP222 to be used for high performance clock distribution in +2.5/3.3 V systems. In a PECL environment series or Thevenin line, terminations are typically used as they require no additional power www.DataSheet4U.com supplies. For more information on using PECL, designers should refer to ... |

| Document |

PDF 143.38KB |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | NB100LVEP221 |

ON Semiconductor |

1:20 Differential HSTL/ECL/PECL Clock Driver |

|

| 2 | NB100LVEP224 |

ON Semiconductor |

1:24 Differential ECL/PECL Clock Driver |

|

| 3 | NB100LVEP17 |

ON Semiconductor |

Quad Differential Driver/Receiver |

|

| 4 | NB100LVEP56 |

ON Semiconductor |

ECL Dual Differential 2:1 Multiplexer |

|

| 5 | NB100LVEP91 |

ON Semiconductor |

2.5 V/3.3 V Any Level Positive Input to -2.5 V/-3.3 V LVNECL Output Translator |

|

| 6 | NB100ELT23L |

ON Semiconductor |

Dual Differential LVPECL/LVDS to LVTTL Translator |

|