Busque con el número de pieza junto con el fabricante o la descripción

ZL30120 |

| Part Number | ZL30120 |

| Manufacturer | Zarlink Semiconductor |

| Description | . . . . 11 1.1 DPLL Features.. .... |

| Features |

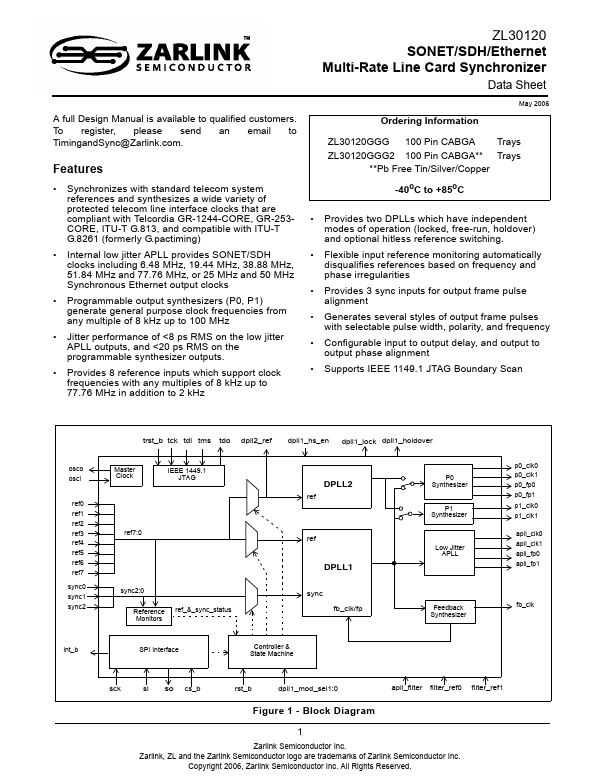

• Synchronizes with standard telecom system references and synthesizes a wide variety of protected telecom line interface clocks that are compliant with Telcordia GR-1244-CORE, GR-253CORE, ITU-T G.813, and compatible with ITU-T G.8261 (formerly G.pactiming) Internal low jitter APLL provides SONET/SDH clocks including 6.48 MHz, 19.44 MHz, 38.88 MHz, 51.84 MHz and 77.76 MHz, or 25 MHz and 50 MHz Synchronous Ethernet output clocks Programmable output synthesizers (P0, P1) generate general purpose clock frequencies from any multiple of 8 kHz up to 100 MHz Jitter performance of <8 ps RMS on the low... |

| Document |

PDF 349.94KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | ZL30121 |

Zarlink Semiconductor |

SONET/SDH Low Jitter System Synchronizer |

|

| 2 | ZL30122 |

Zarlink Semiconductor |

SONET/SDH Low Jitter Line Card Synchronizer |

|

| 3 | ZL30123 |

Zarlink Semiconductor |

Low Jitter Line Card Synchronizer |

|

| 4 | ZL30100 |

Zarlink Semiconductor Inc |

T1/E1 System Synchronizer |

|

| 5 | ZL30101 |

Zarlink Semiconductor Inc |

T1/E1 Stratum 3 System Synchronizer |

|

| 6 | ZL30102 |

Zarlink Semiconductor |

T1/E1 Stratum 4/4E Redundant System Clock Synchronizer |

|