Busque con el número de pieza junto con el fabricante o la descripción

AS4LC1M16S0 |

| Part Number | AS4LC1M16S0 |

| Manufacturer | Alliance Semiconductor |

| Description | Output disable/write mask AS4LC2M8S1 and AS4LC2M8S0 AS4LC1M16S0 and AS4LC1M16S1 DataSheet4U.com VSSQ DQ9 DQ8 VCCQ NC UDQM CLK CKE NC A9 A8 A7 A6 A5 A4 VSS RA0 – 10 DataShee Address inputs CA0 – 7 ... |

| Features |

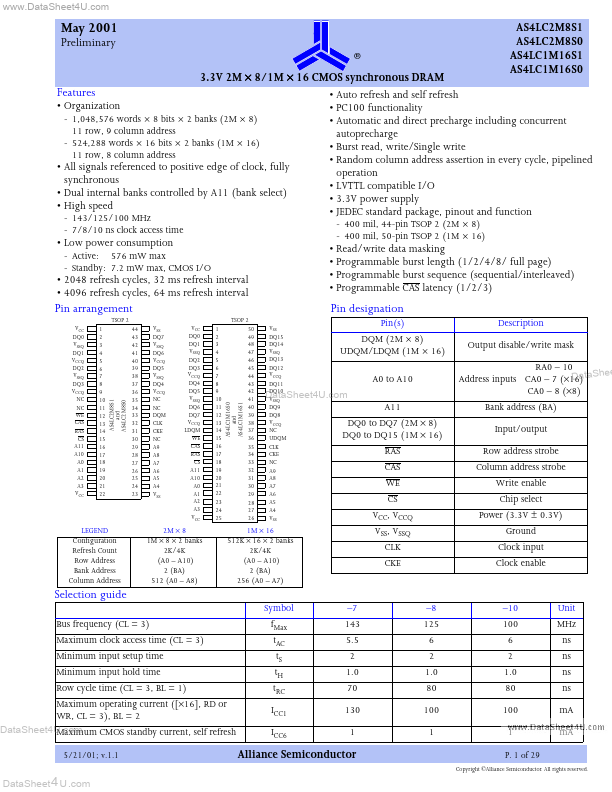

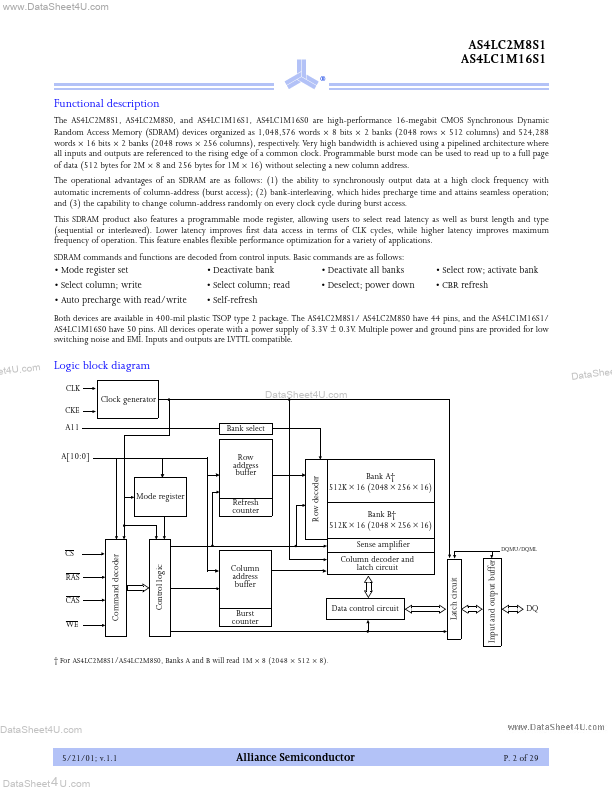

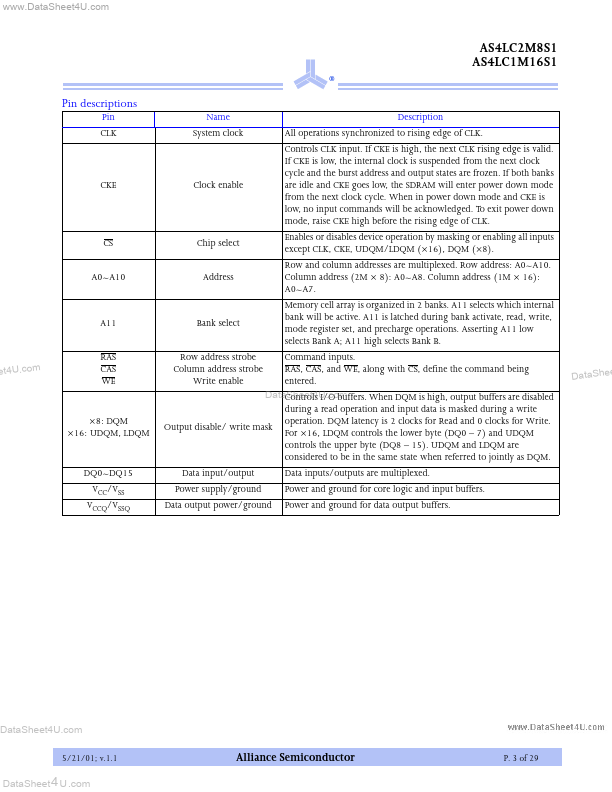

• Organization - 1,048,576 words × 8 bits × 2 banks (2M × 8) 11 row, 9 column address - 524,288 words × 16 bits × 2 banks (1M × 16) 11 row, 8 column address AS4LC2M8S1 AS4LC2M8S0 AS4LC1M16S1 AS4LC1M16S0 • All signals referenced to positive edge of clock, fully synchronous • Dual internal banks controlled by A11 (bank select) • High speed - 143/125/100 MHz - 7/8/10 ns clock access time • Auto refresh and self refresh • PC100 functionality • Automatic and direct precharge including concurrent autoprecharge • Burst read, write/Single write • Random column address assertion in every cycle, pipe... |

| Document |

PDF 1.01MB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | AS4LC1M16S1 |

Alliance Semiconductor |

(AS4LCxMxxSx) 3.3V 2M X 8/1M X 16 CMOS synchronous DRAM |

|

| 2 | AS4LC1M16E5 |

Alliance Semiconductor |

3V 1M x 16 CMOS DRAM |

|

| 3 | AS4LC256K16E0 |

Alliance Semiconductor |

3.3V 256K X 16 CMOS DRAM (EDO) |

|

| 4 | AS4LC2M8S0 |

Alliance Semiconductor |

(AS4LCxMxxSx) 3.3V 2M X 8/1M X 16 CMOS synchronous DRAM |

|

| 5 | AS4LC2M8S1 |

Alliance Semiconductor |

(AS4LCxMxxSx) 3.3V 2M X 8/1M X 16 CMOS synchronous DRAM |

|

| 6 | AS4LC4M16 |

Austin Semiconductor |

4 MEG x 16 DRAM |

|