Busque con el número de pieza junto con el fabricante o la descripción

ST20450 |

| Part Number | ST20450 |

| Manufacturer | STMicroelectronics (https://www.st.com/) |

| Description | language (BSDL) is available. Illegal configuration for strobes If any strobe is configured with edge times of: e1time = 0, e2time = (castime*2) - 1 phases, that strobe will behave erroneously when b... |

| Features |

s

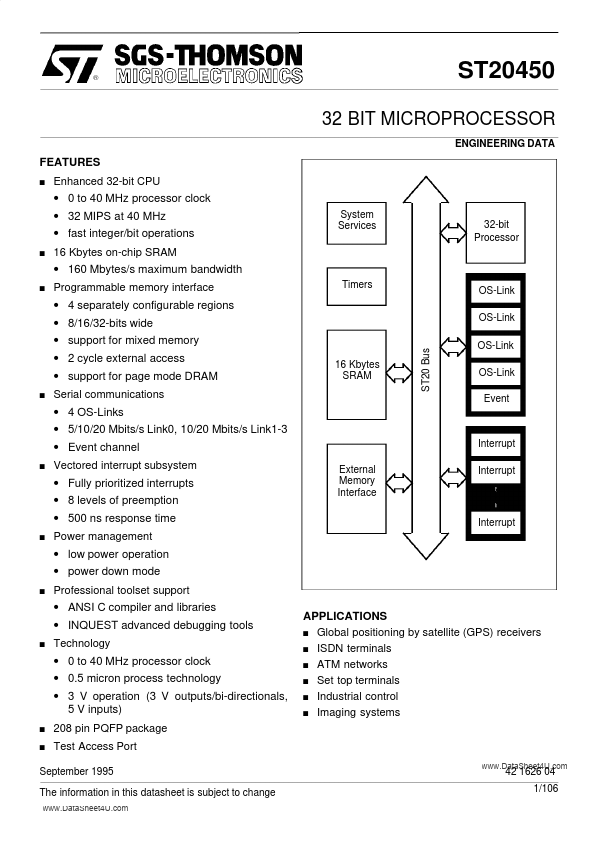

Enhanced 32-bit CPU

• 0 to 40 MHz processor clock • 32 MIPS at 40 MHz • fast integer/bit operations s System Services 32-bit Processor 16 Kbytes on-chip SRAM • 160 Mbytes/s maximum bandwidth s Programmable memory interface Timers OS-Link OS-Link ST20 Bus • 4 separately configurable regions • 8/16/32-bits wide • support for mixed memory • 2 cycle external access • support for page mode DRAM s OS-Link OS-Link Event 16 Kbytes SRAM Serial communications • 4 OS-Links • 5/10/20 Mbits/s Link0, 10/20 Mbits/s Link1-3 • Event channel s Interrupt External Memory Interface Interrupt Vect... |

| Document |

PDF 697.73KB |

Similar Datasheet