Busque con el número de pieza junto con el fabricante o la descripción

74HCT107 |

| Part Number | 74HCT107 |

| Manufacturer | Philips |

| Description | The 74HC/HCT107 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. 74HC/HCT107 The 74HC/HCT1... |

| Features |

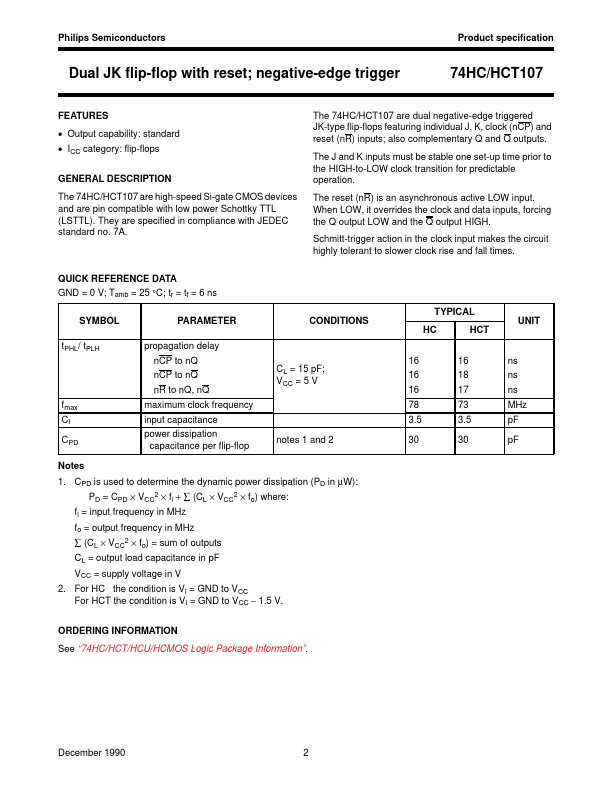

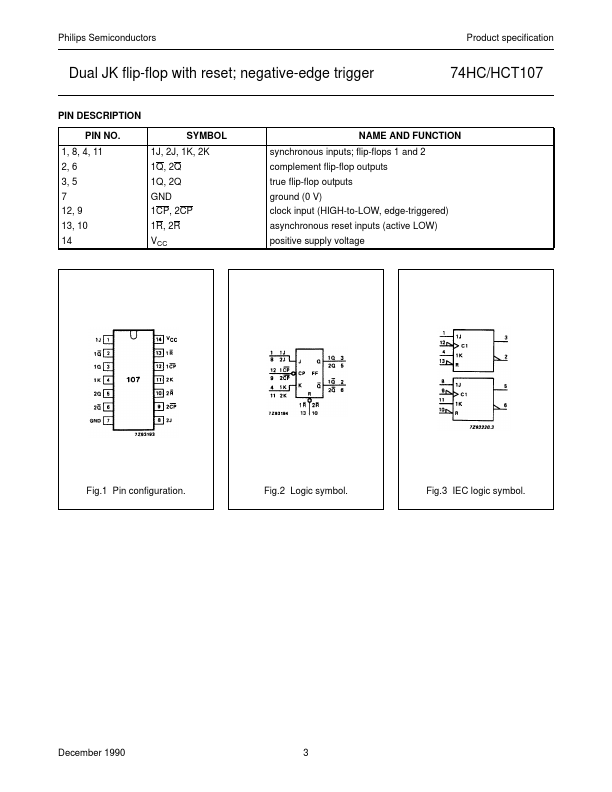

• Output capability: standard • ICC category: flip-flops GENERAL DESCRIPTION The 74HC/HCT107 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A. 74HC/HCT107 The 74HC/HCT107 are dual negative-edge triggered JK-type flip-flops featuring individual J, K, clock (nCP) and reset (nR) inputs; also complementary Q and Q outputs. The J and K inputs must be stable one set-up time prior to the HIGH-to-LOW clock transition for predictable operation. The reset (nR) is an asynchronous active LOW input.... |

| Document |

PDF 53.68KB |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74HCT10 |

Philips |

Triple 3-input NAND gate |

|

| 2 | 74HCT10 |

nexperia |

Triple 3-input NAND gate |

|

| 3 | 74HCT10-Q100 |

nexperia |

Triple 3-input NAND gate |

|

| 4 | 74HCT107 |

nexperia |

Dual JK flip-flop |

|

| 5 | 74HCT107-Q100 |

nexperia |

Dual JK flip-flop |

|

| 6 | 74HCT107D |

nexperia |

Dual JK flip-flop |

|