Busque con el número de pieza junto con el fabricante o la descripción

74HC40104 |

| Part Number | 74HC40104 |

| Manufacturer | Philips |

| Description | The 74HC/HCT40104 are high-speed Si-gate CMOS devices and are pin compatible with the “40104” of the “4000B” series. They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT40104 are ... |

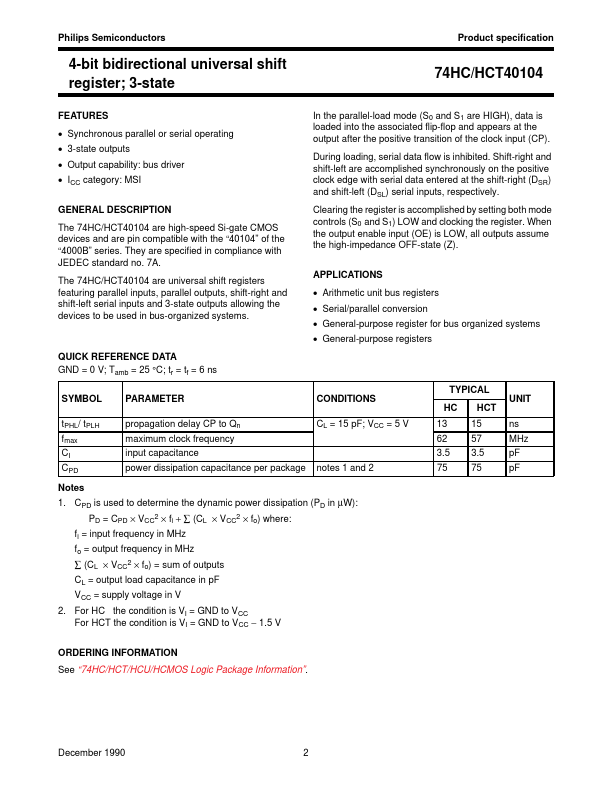

| Features |

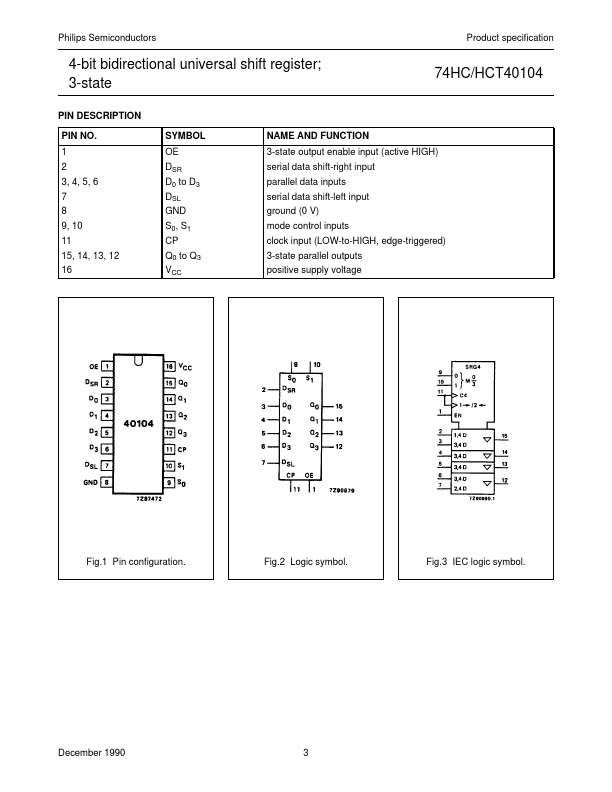

• Synchronous parallel or serial operating • 3-state outputs • Output capability: bus driver • ICC category: MSI GENERAL DESCRIPTION The 74HC/HCT40104 are high-speed Si-gate CMOS devices and are pin compatible with the “40104” of the “4000B” series. They are specified in compliance with JEDEC standard no. 7A. The 74HC/HCT40104 are universal shift registers featuring parallel inputs, parallel outputs, shift-right and shift-left serial inputs and 3-state outputs allowing the devices to be used in bus-organized systems. In the parallel-load mode (S0 and S1 are HIGH), data is loaded into the asso... |

| Document |

PDF 57.35KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74HC40102 |

Philips |

8-bit synchronous BCD down counter |

|

| 2 | 74HC40103 |

NXP |

8-bit synchronous binary down counter |

|

| 3 | 74HC40103 |

nexperia |

8-bit synchronous binary down counter |

|

| 4 | 74HC40103D |

nexperia |

8-bit synchronous binary down counter |

|

| 5 | 74HC40103PW |

nexperia |

8-bit synchronous binary down counter |

|

| 6 | 74HC40105 |

NXP |

4-bit x 16-word FIFO register |

|