Busque con el número de pieza junto con el fabricante o la descripción

MCM63P733A |

| Part Number | MCM63P733A |

| Manufacturer | Motorola |

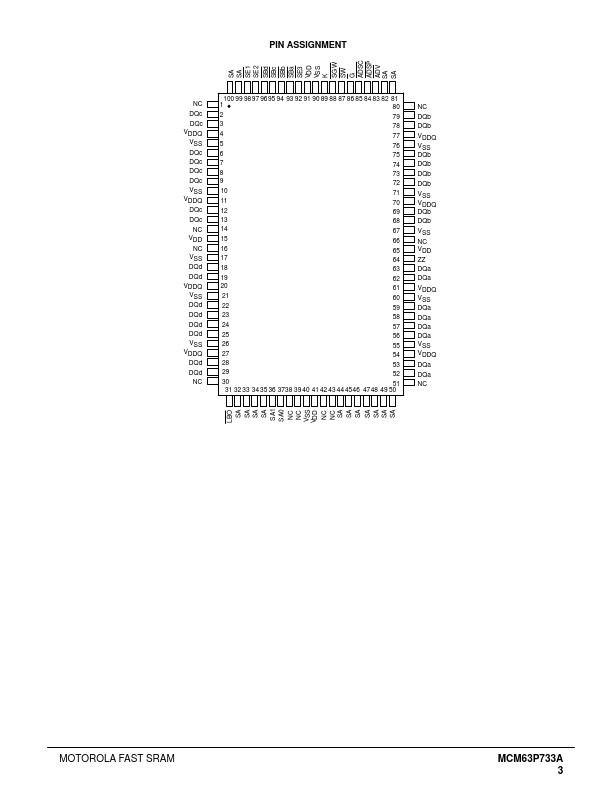

| Description | Pin Locations 85 Symbol ADSC Type Input Description Synchronous Address Status Controller: Active low, interrupts any ongoing burst and latches a new external address. Used to initiate a READ, WRITE,... |

| Features |

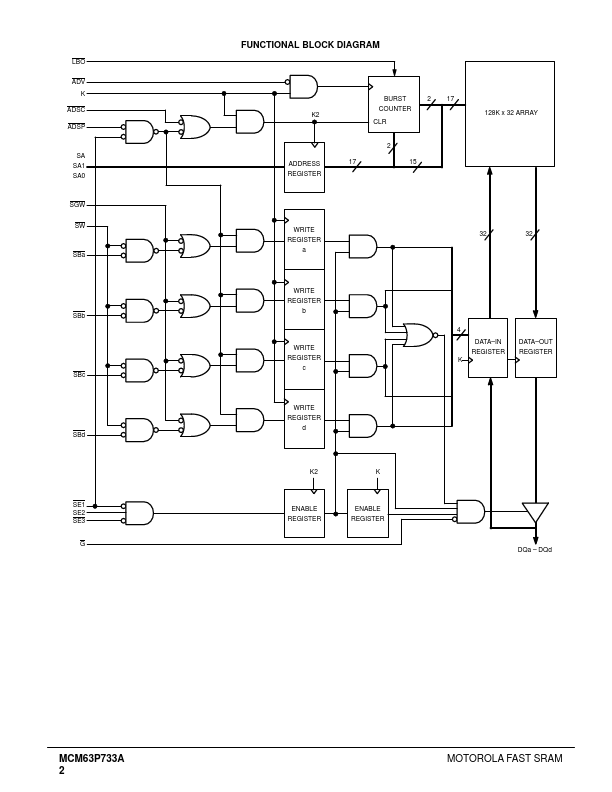

itive –edge –triggered noninverting registers. Bursts can be initiated with either ADSP or ADSC input pins. Subsequent burst addresses can be generated internally by the MCM63P733A (burst sequence operates in linear or interleaved mode dependent upon state of LBO) and controlled by the burst address advance (ADV) input pin. Write cycles are internally self –timed and are initiated by the rising edge of the clock (K) input. This feature eliminates complex off –chip write pulse generation and provides increased timing flexibility for incoming signals. Synchronous byte write (SBx), synchronous global... |

| Document |

PDF 238.09KB |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | MCM63P736 |

Motorola |

128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

|

| 2 | MCM63P531 |

Motorola |

32K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

|

| 3 | MCM63P631 |

Motorola |

64K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

|

| 4 | MCM63P631A |

Motorola |

64K x 32 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

|

| 5 | MCM63P636 |

Motorola |

64K x 36 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

|

| 6 | MCM63P818 |

Motorola |

128K x 36 and 256K x 18 Bit Pipelined BurstRAM Synchronous Fast Static RAM |

|