Busque con el número de pieza junto con el fabricante o la descripción

MCM62110 |

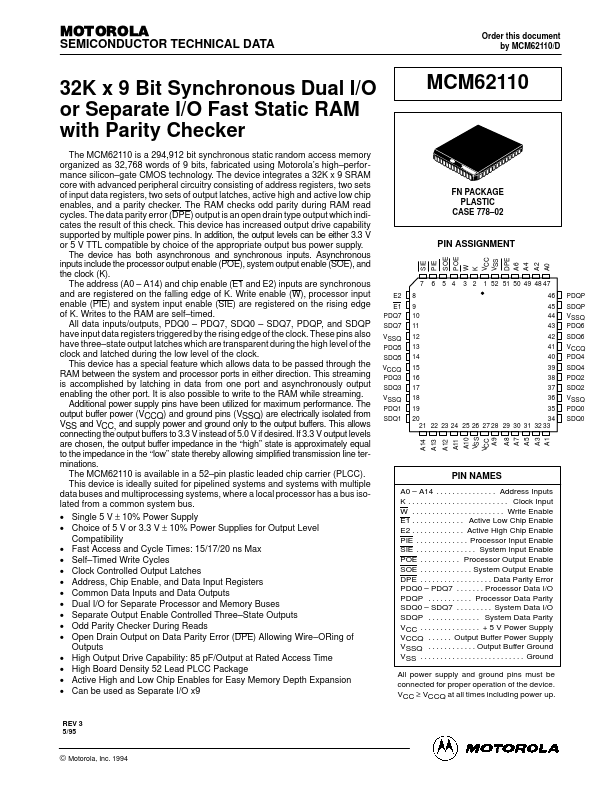

| Part Number | MCM62110 |

| Manufacturer | Motorola |

| Description | MOTOROLA SEMICONDUCTOR TECHNICAL DATA Order this document by MCM62110/D 32K x 9 Bit Synchronous Dual I/O or Separate I/O Fast Static RAM with Parity Checker The MCM62110 is a 294,912 bit synchronou... |

| Features |

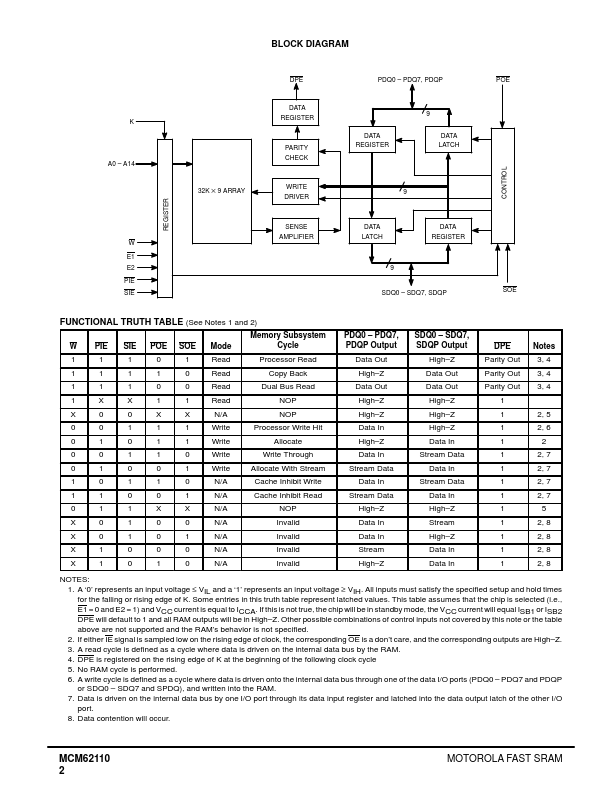

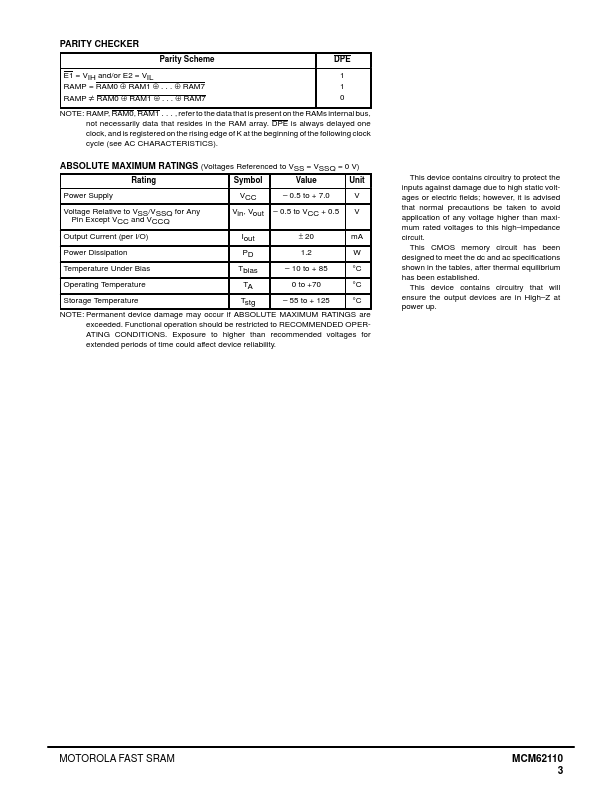

Asynchronous inputs include the processor output enable (POE), system output enable (SOE), and the clock (K). The address (A0 – A14) and chip enable (E1 and E2) inputs are synchronous and are registered on the falling edge of K. Write enable (W), processor input enable (PIE) and system input enable (SIE) are registered on the rising edge of K. Writes to the RAM are self –timed. All data inputs/outputs, PDQ0 – PDQ7, SDQ0 – SDQ7, PDQP, and SDQP have input data registers triggered by the rising edge of the clock. These pins also have three –state output latches which are transparent during the hig... |

| Document |

PDF 206.62KB |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | MCM6205C |

Motorola |

32K x 9 Bit Fast Static RAM |

|

| 2 | MCM6205D |

Motorola |

32K x 9 Bit Fast Static RAM |

|

| 3 | MCM6206BA |

Motorola |

32K x 8 Bit Fast Static RAM |

|

| 4 | MCM6206BB |

Motorola |

32K x 8 Bit Fast Static RAM |

|

| 5 | MCM6206C |

Motorola |

32K x 8-Bit Fast SRAM |

|

| 6 | MCM6206D |

Motorola |

32K x 8 Bit Fast Static RAM |

|