Busque con el número de pieza junto con el fabricante o la descripción

QL2009 |

| Part Number | QL2009 |

| Manufacturer | ETC |

| Description | Pin TDI TRSTB TMS TCK TDO STM I/ACLK I/GCLK I I/O VCC GND Function Test Data In for JTAG Active low Reset for JTAG Test Mode Select for JTAG Test Clock for JTAG Test data out for JTAG Special Test Mo... |

| Features |

-3.3V and 5.0V operation with low standby power -I/O pin-compatibility between different devices in the same packages -PCI compliant (at 5.0V), full speed 33 MHz implementations -High design security provided by security fuses QL2009 Block Diagram

672 Logic Cells

3-35

QL2009

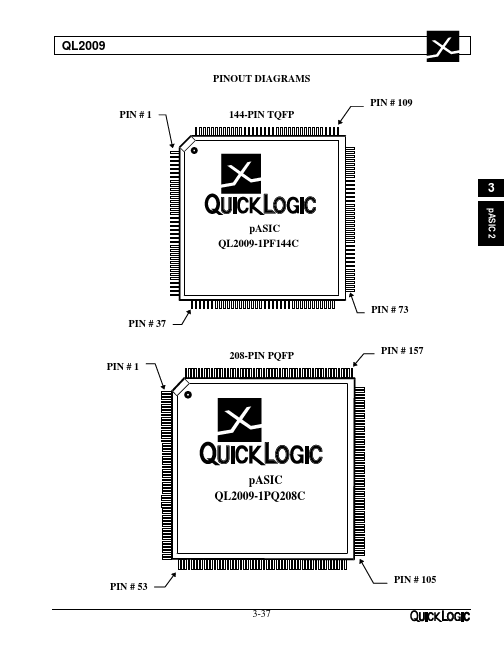

PRODUCT SUMMARY The QL2009 is a 9,000 usable ASIC gate,16,000 usable PLD gate member of the pASIC 2 family of FPGAs. pASIC 2 FPGAs employ a unique combination of architecture, technology, and software tools to provide high speed, high usable density, low price, and flexibility in the same devices. The flexibility and sp... |

| Document |

PDF 272.83KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | QL2003 |

QL |

Low Cost and Flexibility |

|

| 2 | QL2007 |

ETC |

pASIC 2 FPGA Combining Speed |

|

| 3 | QL2009-0PB256C |

ETC |

3.3V and 5.0V pASIC 2 FPGA Combining Speed/ Density/ Low Cost and Flexibility |

|

| 4 | QL2009-0PB256I |

ETC |

3.3V and 5.0V pASIC 2 FPGA Combining Speed/ Density/ Low Cost and Flexibility |

|

| 5 | QL2009-0PF144C |

ETC |

3.3V and 5.0V pASIC 2 FPGA Combining Speed/ Density/ Low Cost and Flexibility |

|

| 6 | QL2009-0PF144I |

ETC |

3.3V and 5.0V pASIC 2 FPGA Combining Speed/ Density/ Low Cost and Flexibility |

|