Busque con el número de pieza junto con el fabricante o la descripción

74F109 |

| Part Number | 74F109 |

| Manufacturer | NXP (https://www.nxp.com/) |

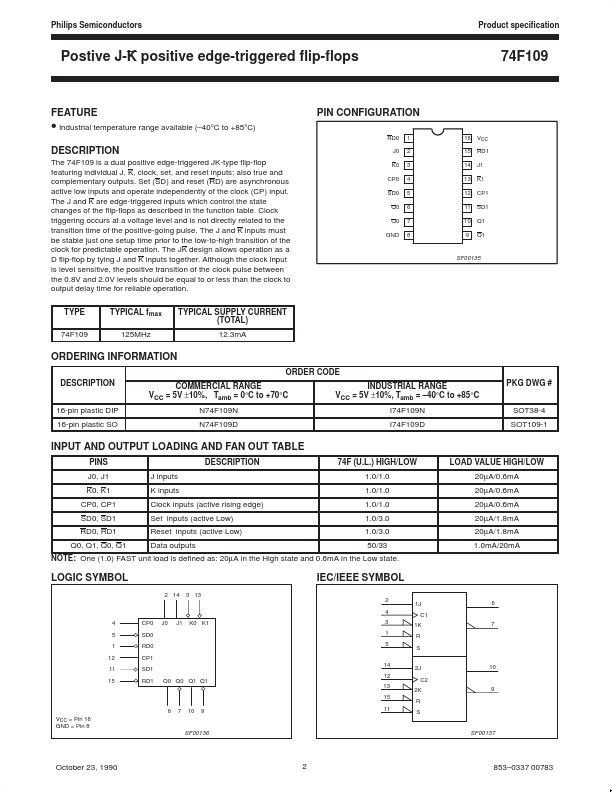

| Description | The 74F109 is a dual positive edge-triggered JK-type flip-flop featuring individual J, K, clock, set, and reset inputs; also true and complementary outputs. Set (SD) and reset (RD) are asynchronous ac... |

| Features |

operation as a D flip-flop by tying J and K inputs together. Although the clock input is level sensitive, the positive transition of the clock pulse between the 0.8V and 2.0V levels should be equal to or less than the clock to output delay time for reliable operation. TYPE 74F109 TYPICAL fmax 125MHz TYPICAL SUPPLY CURRENT (TOTAL) 12.3mA

PIN CONFIGURATION

RD0 J0 K0 CP0 SD0 Q0 Q0 GND 1 2 3 4 5 6 7 8 16 15 14 13 12 11 10 9 VCC RD1 J1 K1 CP1 SD1 Q1 Q1

SF00135

ORDERING INFORMATION

ORDER CODE DESCRIPTION 16-pin plastic DIP 16-pin plastic SO COMMERCIAL RANGE VCC = 5V ±10%, Tamb = 0°C to +70°C N74... |

| Document |

PDF 85.03KB |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74F10 |

NXP |

Triple 3-input NAND gate |

|

| 2 | 74F10 |

Fairchild Semiconductor |

Triple 3-Input NAND Gate |

|

| 3 | 74F10 |

National Semiconductor |

Triple 3-Input NAND Gate |

|

| 4 | 74F10 |

Texas Instruments |

TRIPLE 3-INPUT POSITIVE-NAND GATE |

|

| 5 | 74F1056 |

Fairchild Semiconductor |

8-Bit Schottky Barrier Diode Array |

|

| 6 | 74F1071 |

Fairchild Semiconductor |

18-Bit Undershoot/Overshoot Clamp |

|