Busque con el número de pieza junto con el fabricante o la descripción

DM74LS125A |

| Part Number | DM74LS125A |

| Manufacturer | Fairchild Semiconductor |

| Description | This device contains four independent gates each of which performs a non-inverting buffer function. The outputs have the 3-STATE feature. When enabled, the outputs exhibit the low impedance characteri... |

| Features |

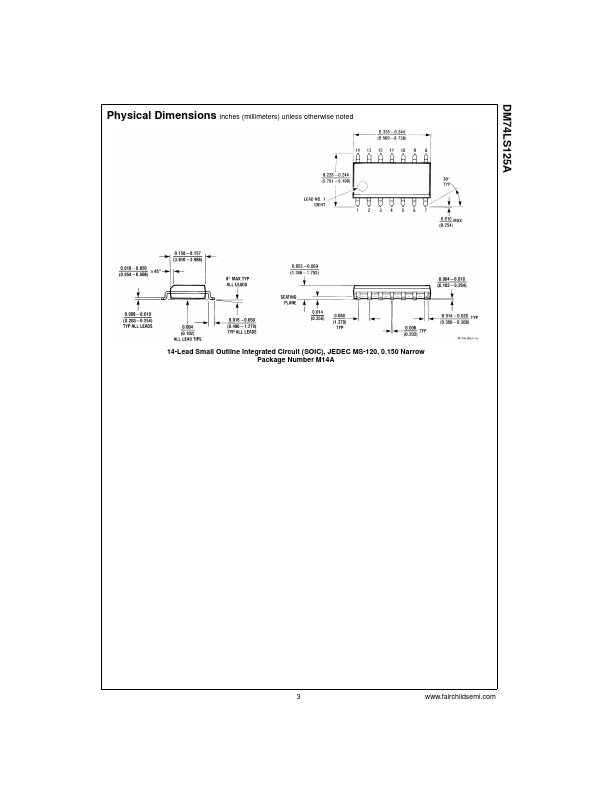

tline Package (SOP), EIAJ TYPE II, 5.3mm Wide 14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

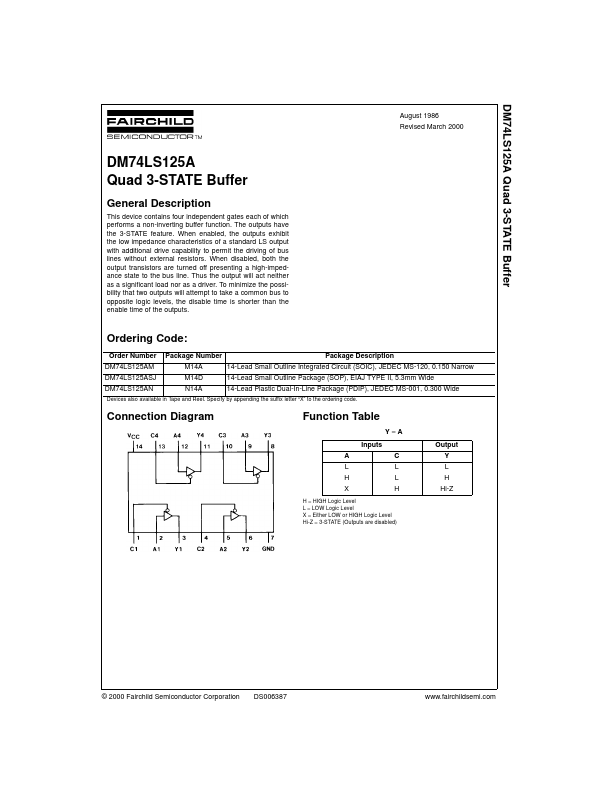

Connection Diagram

Function Table

Y=A Inputs A L H X C L L H Output Y L H Hi-Z

H = HIGH Logic Level L = LOW Logic Level X = Either LOW or HIGH Logic Level Hi-Z = 3-STATE (Outputs are disabled)

© 2000 Fairchild Semiconductor Corporation

DS006387

www.fairchildsemi.com

DM74LS125A

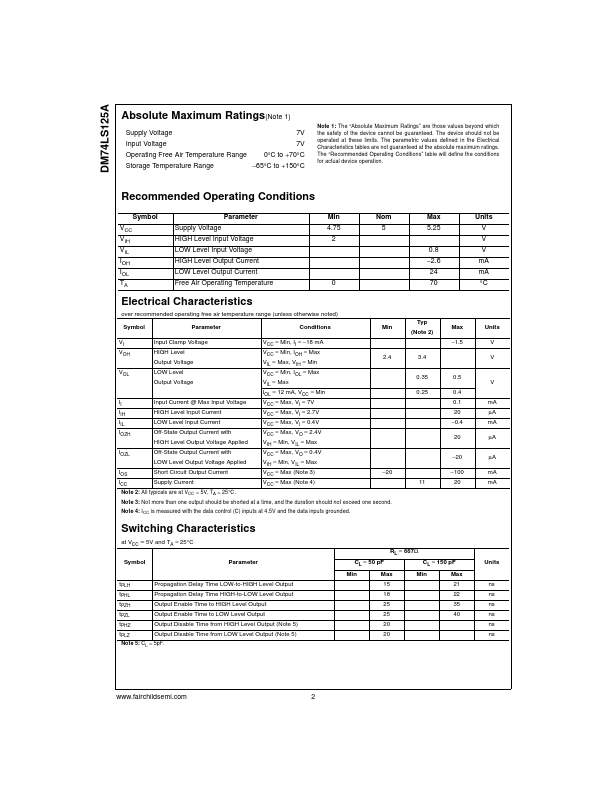

Absolute Maximum Ratings(Note 1)

Supply Voltage Input Voltage Operating Free Air Temperatur... |

| Document |

PDF 62.34KB |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | DM74LS125A |

National Semiconductor |

Quad TRI-STATE Buffers |

|

| 2 | DM74LS123 |

Fairchild Semiconductor |

Dual Retriggerable One-Shot |

|

| 3 | DM74LS126A |

Fairchild Semiconductor |

Quad 3-STATE Buffer |

|

| 4 | DM74LS10 |

Fairchild Semiconductor |

Triple 3-Input NAND Gate |

|

| 5 | DM74LS10 |

National Semiconductor |

Triple 3-Input NAND Gates |

|

| 6 | DM74LS107A |

National Semiconductor |

Dual Negative-Edge- Triggered Master-Slave J-K Flip-Flops |

|