Busque con el número de pieza junto con el fabricante o la descripción

DM7476 |

| Part Number | DM7476 |

| Manufacturer | Fairchild Semiconductor |

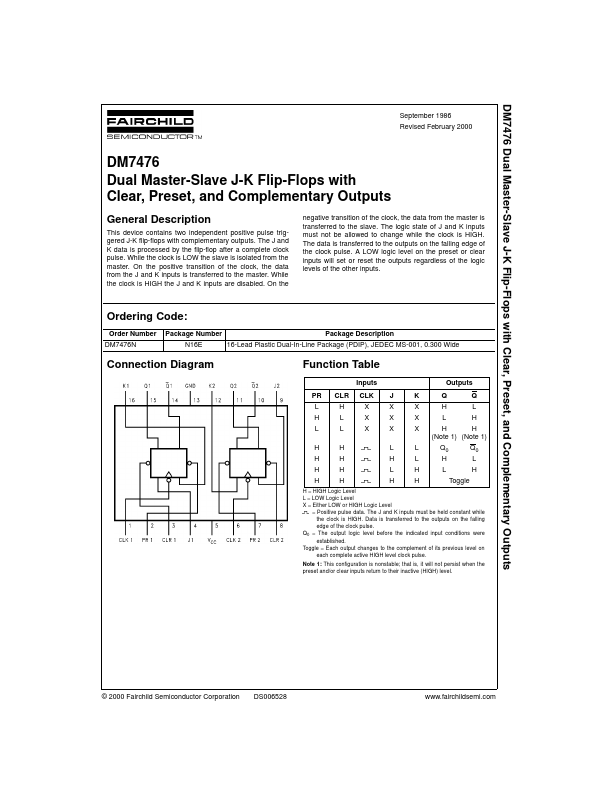

| Description | This device contains two independent positive pulse triggered J-K flip-flops with complementary outputs. The J and K data is processed by the flip-flop after a complete clock pulse. While the clock is... |

| Features |

levels of the other inputs.

Ordering Code:

Order Number DM7476N Package Number N16E Package Description 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Connection Diagram

Function Table

Inputs PR L H L H H H H CLR H L L H H H H CLK X X X J X X X L H L H K X X X L L H H Outputs Q H L Q L H

H = HIGH Logic Level L = LOW Logic Level X = Either LOW or HIGH Logic Level = Positive pulse data. The J and K inputs must be held constant while the clock is HIGH. Data is transferred to the outputs on the falling edge of the clock pulse. Q0 = The output logic level before the indi... |

| Document |

PDF 41.28KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | DM7470 |

National Semiconductor |

AND Gated Positive Edge Triggered J-K Flip-Flop |

|

| 2 | DM7473 |

Fairchild Semiconductor |

Dual Master-Slave J-K Flip-Flop |

|

| 3 | DM7474 |

Fairchild Semiconductor |

Dual Positive-Edge-Triggered D-Type Flip-Flop |

|

| 4 | DM7474 |

National Semiconductor |

Dual Positive-Edge-Triggered D Flip-Flops |

|

| 5 | DM7474M |

Fairchild Semiconductor |

Dual Positive-Edge-Triggered D-Type Flip-Flop |

|

| 6 | DM7474N |

Fairchild Semiconductor |

Dual Positive-Edge-Triggered D-Type Flip-Flop |

|