Busque con el número de pieza junto con el fabricante o la descripción

MK2049-36 |

| Part Number | MK2049-36 |

| Manufacturer | Renesas (https://www.renesas.com/) |

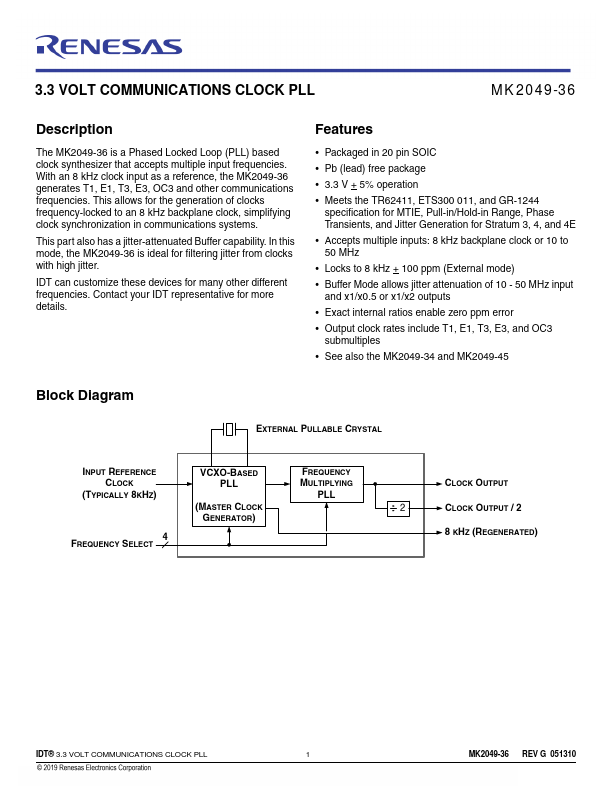

| Description | The MK2049-36 is a Phased Locked Loop (PLL) based clock synthesizer that accepts multiple input frequencies. With an 8 kHz clock input as a reference, the MK2049-36 generates T1, E1, T3, E3, OC3 and o... |

| Features |

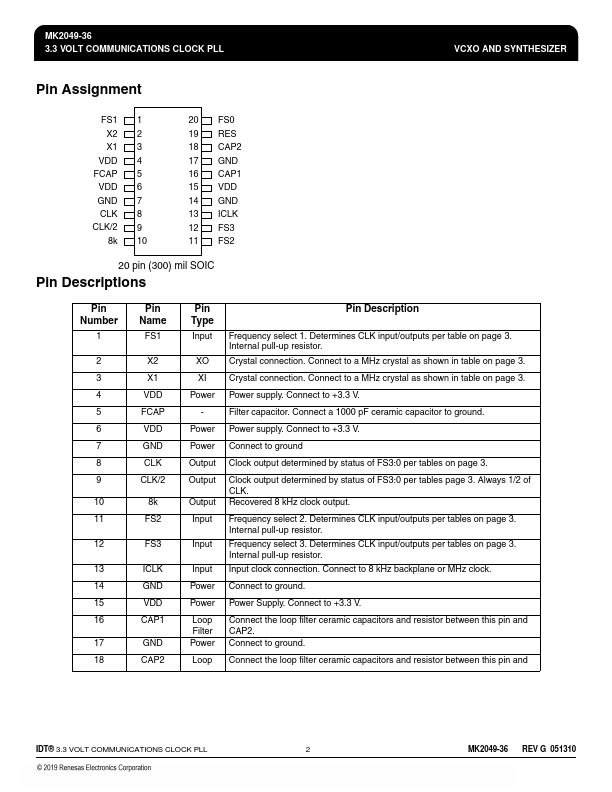

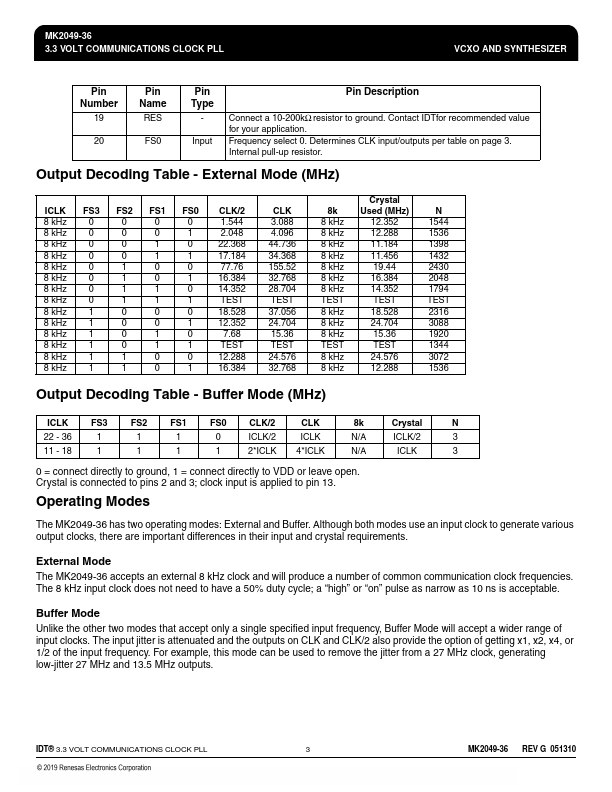

• Packaged in 20 pin SOIC • Pb (lead) free package • 3.3 V + 5% operation • Meets the TR62411, ETS300 011, and GR-1244 specification for MTIE, Pull-in/Hold-in Range, Phase Transients, and Jitter Generation for Stratum 3, 4, and 4E • Accepts multiple inputs: 8 kHz backplane clock or 10 to 50 MHz • Locks to 8 kHz + 100 ppm (External mode) • Buffer Mode allows jitter attenuation of 10 - 50 MHz input and x1/x0.5 or x1/x2 outputs • Exact internal ratios enable zero ppm error • Output clock rates include T1, E1, T3, E3, and OC3 submultiples • See also the MK2049-34 and MK2049-45 Block Diagram EXTE... |

| Document |

PDF 215.82KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | MK2049-34 |

Integrated Circuit Systems |

3.3 V Communications Clock PLL |

|

| 2 | MK2049-34 |

Renesas |

CLOCK VCXO PLL |

|

| 3 | MK2049-34A |

Integrated Circuit Systems |

3.3 Volt Communications Clock VCXO PLL |

|

| 4 | MK2049-35 |

Integrated Circuit Systems |

3.3 V Communications Clock PLL |

|

| 5 | MK2049-36 |

Integrated Circuit Systems |

3.3 V Communications Clock PLL |

|

| 6 | MK2049-01 |

Integrated Circuit Systems |

Communications Clock PLL |

|