Busque con el número de pieza junto con el fabricante o la descripción

74HC107 |

| Part Number | 74HC107 |

| Manufacturer | nexperia (https://www.nexperia.com/) |

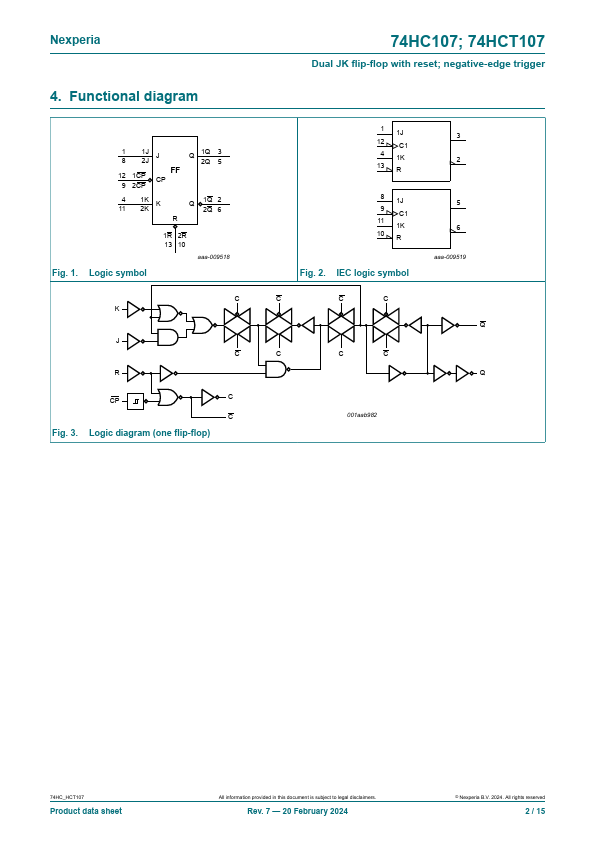

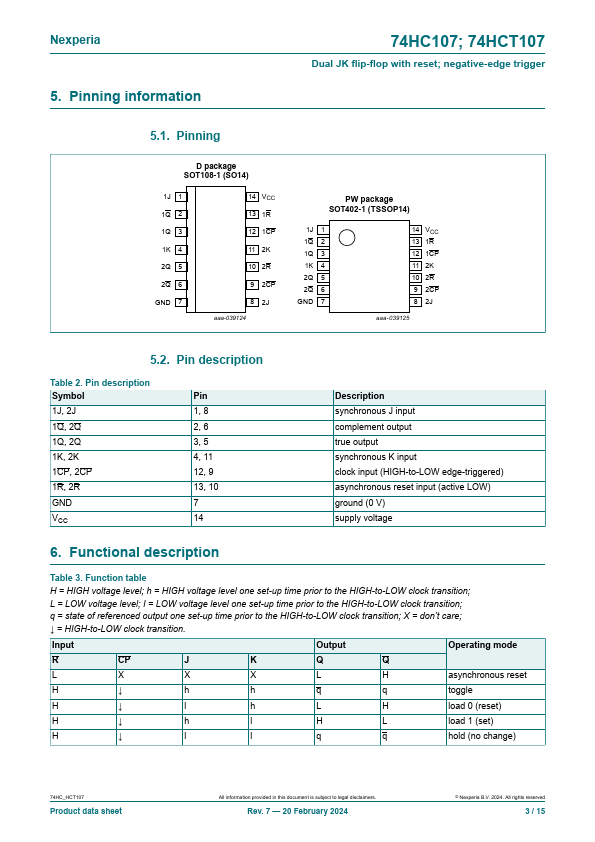

| Description | The 74HC107; 74HCT107 is a dual negative edge triggered JK flip-flop featuring individual J and K inputs, clock (CP) and reset (R) inputs and complementary Q and Q outputs. The reset is an asynchronou... |

| Features |

• Wide supply voltage range from 2.0 V to 6.0 V • CMOS low power dissipation • High noise immunity • Latch-up performance exceeds 100 mA per JESD 78 Class II Level B • Complies with JEDEC standards: • JESD8C (2.7 V to 3.6 V) • JESD7A (2.0 V to 6.0 V) • Input levels: • The 74HC107: CMOS levels • The 74HCT107: TTL levels • ESD protection: • HBM: ANSI/ESDA/JEDEC JS-001 class 2 exceeds 2000 V • CDM: ANSI/ESDA/JEDEC JS-002 class C3 exceeds 1000 V • Specified from -40 °C to +85 °C and from -40 °C to +125 °C 3. Ordering information Table 1. Ordering information Type number Package Temperature rang... |

| Document |

PDF 262.00KB |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74HC10 |

Philips |

Triple 3-input NAND gate |

|

| 2 | 74HC10 |

Texas Instruments |

Triple 3-Input NAND Gates |

|

| 3 | 74HC10 |

nexperia |

Triple 3-input NAND gate |

|

| 4 | 74HC10-Q100 |

nexperia |

Triple 3-input NAND gate |

|

| 5 | 74HC107 |

Philips |

Dual JK flip-flop |

|

| 6 | 74HC107-Q100 |

nexperia |

Dual JK flip-flop |

|