Busque con el número de pieza junto con el fabricante o la descripción

74AUP2G80 |

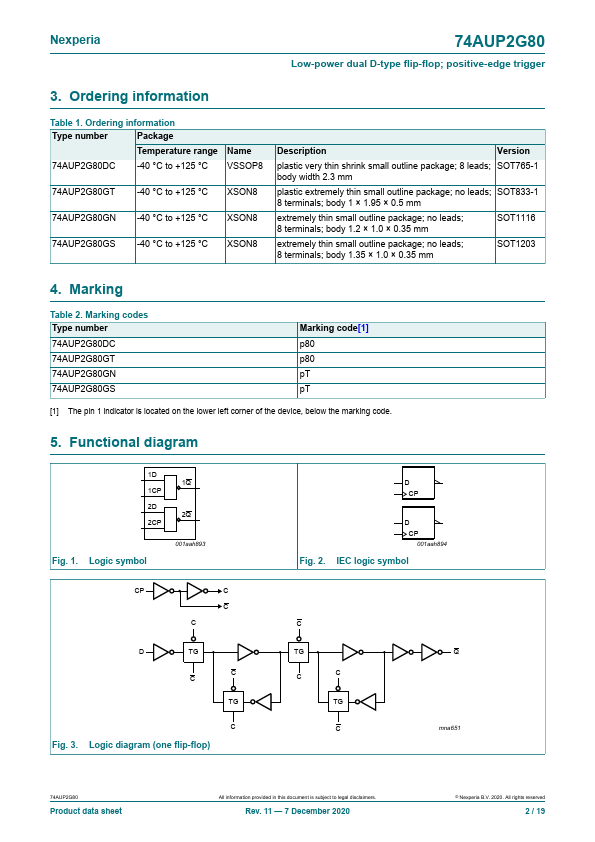

| Part Number | 74AUP2G80 |

| Manufacturer | nexperia (https://www.nexperia.com/) |

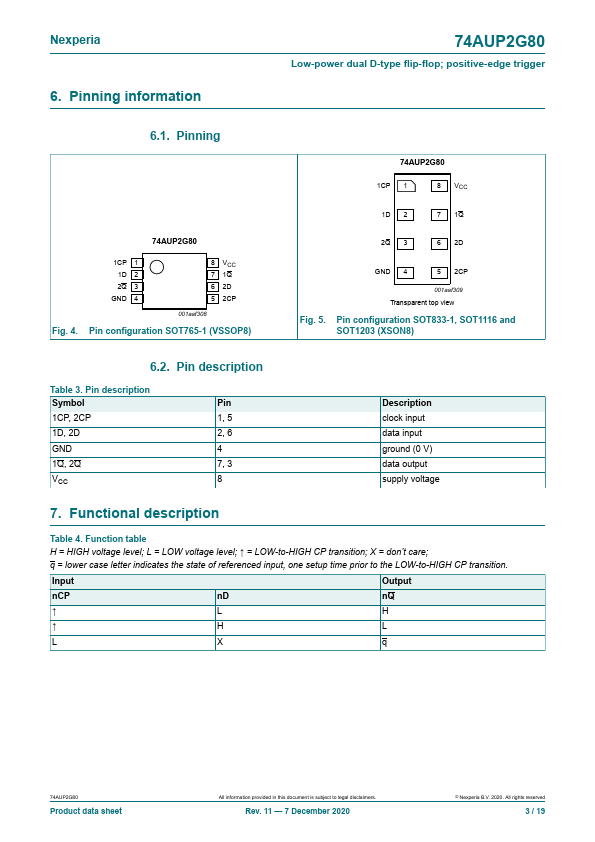

| Description | The 74AUP2G80 provides the dual positive-edge triggered D-type flip-flop. Information on the data input is transferred to the Q output on the LOW-to-HIGH transition of the clock pulse. The input pin D... |

| Features |

• Wide supply voltage range from 0.8 V to 3.6 V • High noise immunity • Complies with JEDEC standards: • JESD8-12 (0.8 V to 1.3 V) • JESD8-11 (0.9 V to 1.65 V) • JESD8-7 (1.2 V to 1.95 V) • JESD8-5 (1.8 V to 2.7 V) • JESD8-B (2.7 V to 3.6 V) • ESD protection: • HBM JESD22-A114F Class 3A exceeds 5 000 V • MM JESD22-A115-A exceeds 200 V • CDM JESD22-C101E exceeds 1 000 V • Low static power consumption; ICC = 0.9 μA (maximum) • Latch-up performance exceeds 100 mA per JESD78 Class II • Inputs accept voltages up to 3.6 V • Low noise overshoot and undershoot < 10 % of VCC • IOFF circuitry provides p... |

| Document |

PDF 274.87KB |

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | 74AUP2G80 |

NXP |

Low-power dual D-type flip-flop |

|

| 2 | 74AUP2G86 |

NXP |

Low Power Dual 2-Input EXCLUSIVE Gate |

|

| 3 | 74AUP2G86 |

Diodes |

DUAL EXCLUSIVE OR GATE |

|

| 4 | 74AUP2G86 |

nexperia |

Low-power dual 2-input EXCLUSIVE-OR gate |

|

| 5 | 74AUP2G00 |

NXP |

Low-power dual 2-input NAND gate |

|

| 6 | 74AUP2G00 |

Diodes |

DUAL NAND GATE |

|