Busque con el número de pieza junto con el fabricante o la descripción

CY7C1303BV18 |

| Part Number | CY7C1303BV18 |

| Manufacturer | Cypress Semiconductor |

| Description | • Separate independent Read and Write data ports — Supports concurrent transactions • 167-MHz Clock for high bandwidth — 2.5 ns Clock-to-Valid access time • 2-Word Burst on all accesses • Double Data... |

| Features |

Functional Description

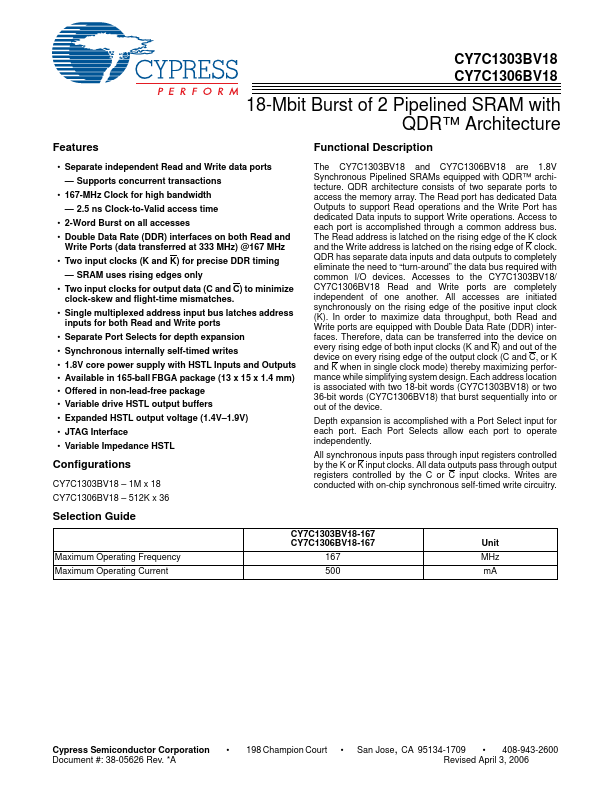

• Separate independent Read and Write data ports — Supports concurrent transactions • 167-MHz Clock for high bandwidth — 2.5 ns Clock-to-Valid access time • 2-Word Burst on all accesses • Double Data Rate (DDR) interfaces on both Read and Write Ports (data transferred at 333 MHz) @167 MHz • Two input clocks (K and K) for precise DDR timing — SRAM uses rising edges only • Two input clocks for output data (C and C) to minimize clock-skew and flight-time mismatches. • Single multiplexed address input bus latches address inputs for both Read and Write ports • Separate Port... |

| Document |

PDF 677.60KB |

Similar Datasheet

| No. | Parte # | Fabricante | Descripción | Hoja de Datos |

|---|---|---|---|---|

| 1 | CY7C1303BV25 |

Cypress Semiconductor |

18-Mbit Burst of Two-Pipelined SRAM |

|

| 2 | CY7C130 |

Cypress Semiconductor |

1K x 8 Dual-Port Static RAM |

|

| 3 | CY7C1302CV25 |

Cypress Semiconductor |

9-Mbit Burst of Two Pipelined SRAMs |

|

| 4 | CY7C1302DV25 |

Cypress Semiconductor |

9-Mbit Burst of Two Pipelined SRAMs |

|

| 5 | CY7C1304DV25 |

Cypress Semiconductor |

9-Mbit Burst of 4 Pipelined SRAM |

|

| 6 | CY7C1305BV18 |

Cypress Semiconductor |

18-Mbit Burst of 4 Pipelined SRAM |

|